# cādence<sup>®</sup>

## SystemSI – Parallel Bus Analysis Tutorial

Product Version 16.6 July 2014 © 2014 Cadence Design Systems, Inc. All rights reserved.

Cadence Design Systems, Inc. (Cadence), 2655 Seely Ave., San Jose, CA 95134, USA.

Open SystemC, Open SystemC Initiative, OSCI, SystemC, and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.

**Trademarks:** Trademarks and service marks of Cadence Design Systems, Inc. contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 800.862.4522. All other trademarks are the property of their respective holders.

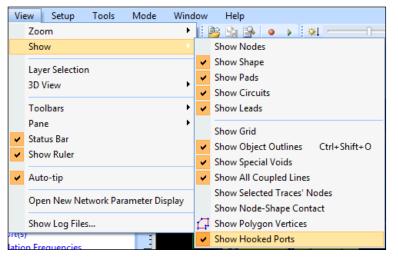

**Restricted Permission:** This publication is protected by copyright law and international treaties and contains trade secrets and proprietary information owned by Cadence. Unauthorized reproduction or distribution of this publication, or any portion of it, may result in civil and criminal penalties. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. Unless otherwise agreed to by Cadence in writing, this statement grants Cadence customers permission to print one (1) hard copy of this publication subject to the following conditions:

- 1. The publication may be used only in accordance with a written agreement between Cadence and its customer.

- 2. The publication may not be modified in any way.

- Any authorized copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement.

- 4. The information contained in this document cannot be used in the development of like products or software, whether for internal or external use, and shall not be used for the benefit of any other party, whether or not for consideration.

**Disclaimer:** Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

**Restricted Rights:** Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

## **Table of Contents**

| 1 | Paral | lel Bus Analysis Tutorial                                 | 6          |

|---|-------|-----------------------------------------------------------|------------|

|   | 1.1   | Overview                                                  |            |

|   | 1.2   | Tutorial Description                                      | 6          |

| 2 | Quicl | s Start                                                   | 7          |

|   | 2.1   | Overview                                                  | 7          |

|   | 2.2   | Open a Template                                           | 7          |

|   | 2.3   | Editing Components                                        | 9          |

|   | 2.3.1 | PCB Block                                                 | 9          |

|   | 2.3.2 | Controller / Memory Block                                 |            |

|   | 2.3   | .2.1 MCP Generation for Controller and Memory IBIS Blocks | . 13       |

|   | 2.3.3 | EBD Block                                                 |            |

|   |       | .3.1 EBD File                                             |            |

|   | 2.3   | .3.2 Using EBD Models in System SI                        |            |

|   | 2.3.4 | S Parameter Block                                         |            |

|   |       | .4.1 Add S Parameter Block                                |            |

|   |       | .4.2 Load S Parameter File                                |            |

|   |       | .4.3 Extract the BBS Model                                |            |

|   |       | .4.4 Load the BBS Model                                   |            |

|   |       | .4.5 Switch the Models                                    |            |

|   | 2.3.5 | VRM Block                                                 |            |

|   | 2.4   | Adding New Components                                     |            |

|   | 2.5   | Setting up Probe Points                                   |            |

|   | 2.6   | Setting up the Simulation                                 |            |

|   | 2.7   | Running the Simulation                                    |            |

| 3 | 2.8   | Custom Templates                                          |            |

| 3 | 3.1   | File Augmentation                                         |            |

|   | 3.2   | Overview<br>IBIS Resources                                |            |

|   | 3.3   | Bus Definition                                            |            |

|   | 3.4   | Pin Mapping                                               |            |

|   | 3.5   | IBIS File GUI                                             |            |

|   | 3.5.1 | Open a Template Project                                   |            |

|   | 3.5.2 | Editing the Controller IBIS                               |            |

|   | 3.5.3 | Pin Mapping                                               |            |

|   | 3.5.4 | Supported IBIS Keywords                                   |            |

| 4 |       | n Entry                                                   |            |

|   | 4.1   | Overview                                                  |            |

|   | 4.2   | Parallel Bus Analysis Templates                           |            |

|   | 4.2.1 | Rank Definition                                           |            |

|   | 4.3   | Parallel Bus Analysis Wizard                              | . 46       |

| 5 | Assig | ning Device Models                                        |            |

|   | 5.1   | Overview                                                  |            |

|   | 5.2   | Design Files                                              | . 51       |

|   | 5.3   | Controller Model                                          | . 52       |

|   | 5.3.1 | Assign the Controller IBIS Model                          | . 52       |

|   | 5.3.2 | Controller Bus Definition                                 | . 54       |

|   | 5.4   | Adding Memory Device Models                               |            |

| 6 | Inter | connect Models                                            |            |

|   | 6.1   | Introduction                                              | . 60       |

|   | 6.2   | Design Files                                              |            |

|   | 6.3   | PCB Model Generation                                      | <b>C</b> 0 |

|   | 6.3.1      | PCB Block Editing6                      | 51 |

|---|------------|-----------------------------------------|----|

|   | 6.3        | .1.1 Layout Extraction Tab              | 51 |

|   | 6.3.2      | PowerSI Model Extraction                | 53 |

|   | 6.3.3      | Assign PowerSI Model                    | 56 |

|   | 6.4        | Package Models                          |    |

|   | 6.4.1      | Controller and Memory Package Model     | 59 |

| 7 | Addiı      | ng a VRM7                               | 70 |

|   | 7.1        | Overview                                | 70 |

|   | 7.2        | Design Files                            | 70 |

|   |            | Define the VRM Block                    |    |

| 8 |            | ecting the System7                      |    |

|   | 8.1        | Introduction                            |    |

|   | 8.1.1      | Example Files7                          |    |

|   |            | Connection Definitions                  |    |

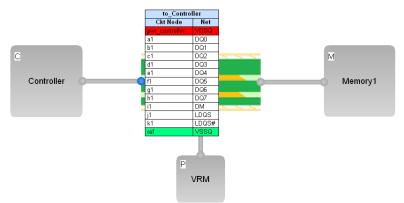

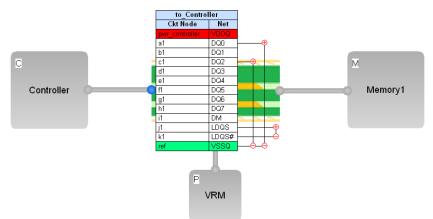

|   | 8.2.1      | Memory Component                        |    |

|   | 8.2.2      | Connecting Controller Component         | 79 |

|   | 8.2.3      | Editing the VRM Block                   |    |

| ~ | 8.2.4      | Unmapped Pins in MCP Editor             |    |

| 9 |            | lation                                  |    |

|   | 9.1        | Introduction                            |    |

|   | 9.2        | Tutorial Files                          |    |

|   | 9.3        | Analysis Options                        |    |

|   | 9.4<br>9.5 | Simulator                               |    |

|   |            | Simulation Configuration                |    |

|   |            | .1.1 Eye Distribution Methods           |    |

|   |            | 1.1.2 BER_Eyes                          |    |

|   |            | Stimulus Definition and Model Selection |    |

|   | 9.7.1      | Controller Setup                        |    |

|   | 9.7.1      | Memory Setup                            |    |

|   | 9.7.2      | Timing Budget                           |    |

|   |            | .3.1 Timing Parameters Definition       |    |

|   |            | .3.2 Stimulus Offset Options            |    |

|   |            | Restore Defaults                        |    |

|   |            | Simulation                              |    |

|   |            | Explore Sweep Manager                   |    |

|   |            | .1.1 Sweep Type                         |    |

|   | 9.9        | .1.2 Sweep List                         |    |

|   |            | .1.3 Total Iterations                   |    |

|   | 9.9        | .1.4 Results                            | )6 |

|   | 9.9        | .1.5 Grouping Parameters                | )7 |

|   | 9.9        | .1.6 Model Sweep                        | )8 |

|   | 9.9.2      | Initial Simulation10                    |    |

|   | 9.9.3      | Running Multiple Sweep11                | 11 |

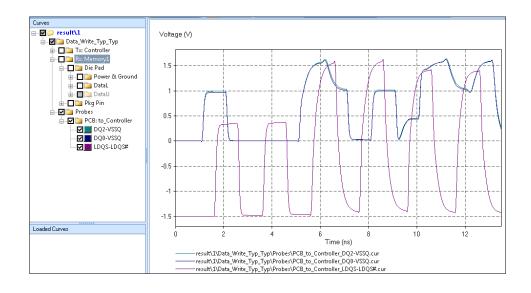

|   | 9.9.4      | Data Presentation / 2D Curve Viewer11   |    |

|   | 9.9.5      | Simulation Directory11                  | 15 |

|   | 9.10       | Additional Exercises                    |    |

|   | 9.10.1     | •                                       |    |

|   | 9.10.2     |                                         |    |

|   | 9.10.3     | e                                       |    |

|   | 9.10.4     |                                         |    |

|   | 9.10.5     | 6                                       |    |

|   |            | 0.5.1 Memory Bus in Write Mode          |    |

|   | 9.1        | 0.5.2 Memory Bus in Read Mode12         | 25 |

|    | 9.10.6  | Terminate Unconnected Nodes                                  |     |

|----|---------|--------------------------------------------------------------|-----|

|    | 9.10.7  | Frequency Response                                           |     |

|    | 9.10.8  | S-Parameter Extraction                                       |     |

|    | 9.10.8  | .1 Single-ended Mode                                         | 130 |

|    | 9.10.8  | .2 Differential Mode                                         |     |

|    | 9.10.9  | S-Parameter View                                             | 134 |

|    | 9.10.10 | Result Browser and 2D Curve Presentation                     | 136 |

|    | 9.10.1  | 0.1 Result Browser                                           | 136 |

|    | 9.10.1  | 0.2 Curve Pane Context Menu                                  | 137 |

|    | 9.10.11 | General Options                                              | 138 |

| 10 | DDR Me  | easurement Report                                            |     |

| -  |         | roduction                                                    |     |

| 1  | 0.2 Tu  | torial Files                                                 | 140 |

| 1  |         | nulation Results                                             |     |

| 1  |         | OR Report Settings                                           |     |

| 1  |         | tup and Hold Derating Tables                                 |     |

| 1  |         | DR4 Threshold                                                |     |

| 1  |         | DDR2 and LPDDR3 Threshold Application                        |     |

| 1  |         | nerate the Report                                            |     |

| 1  |         | port Contents                                                |     |

|    | 10.9.1  | Table of Contents                                            |     |

|    | 10.9.2  | Section 1 – General Information                              |     |

|    | 10.9.3  | Section 2 – Simulation Setup                                 |     |

|    | 10.9.4  | Section 3 – DDR Measurement Setup                            |     |

|    | 10.9.5  | Section 4 – Results                                          |     |

|    | 10.9.5  |                                                              |     |

|    | 10.9.5  |                                                              |     |

|    | 10.9.5  | 8 1                                                          |     |

|    | 10.9.5  |                                                              |     |

|    | 10.9.5  |                                                              |     |

|    | 10.9.5  |                                                              |     |

|    | 10.9.5  | 5 1                                                          |     |

|    | 10.9.6  | Appendix                                                     |     |

| 11 | •       | I with Other Tools                                           |     |

|    |         | stemSI Integration with Allegro Signal Explorer (SigXplorer) |     |

|    |         | stemSI Integration with TimingDesigner                       |     |

| 1  | 1.3 Au  | to Archive SSI Project                                       | 177 |

|    |         |                                                              |     |

| A APPENDIX: BATCH MODE SUPPORT |  |

|--------------------------------|--|

|--------------------------------|--|

182

## 1 Parallel Bus Analysis Tutorial

## 1.1 Overview

Sigrity **SystemSI – Parallel Bus Analysis** is a system-level signal integrity (SI) analysis tool, focused on high speed parallel interfaces. It is integrated with Sigrity patented board and package modeling tools including PowerSI for extraction of accurate hardware interconnect models including real power distribution networks.

**Parallel Bus Analysis** supports HSPICE transistor-level and IBIS behavioral I/O models, including power-aware constructs from BIRD95 and BIRD98, to enable simulations with non-ideal power conditions. Interconnects like connectors and cables can be included with S-parameter data, or SPICE compatible circuit models.

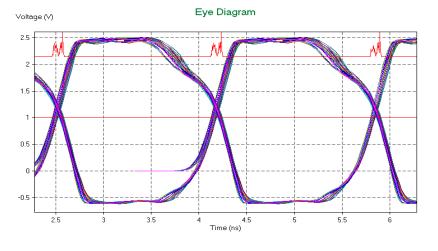

Synchronous design performance metrics including eye diagrams with detailed timing measurements are available as outputs.

## 1.2 Tutorial Description

This tutorial covers the typical steps a user will go through to enter, edit and simulate a parallel bus interface.

- Chapter 2 has a **Quick Start Guide** that uses one of the simulation templates to introduce the **User Interface** and **Design Flow** for **Parallel Bus Analysis**.

- Chapter 3 provides reference information including IBIS file details.

- Chapters 4 through 9 provide a step-by-step overview on how to use **Parallel Bus Analysis** for a DDR3 system.

- Chapter 10 has advanced topics.

Files can be classified into two types: Templates and Samples.

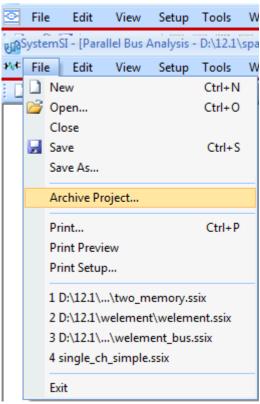

- The template files for Chapter 2 and 3 are easily accessible from the GUI, through the File menu.

- The Sample files for Chapter 4 through 9 are in the \Samples\SystemSI\Parallel Bus Analysis\Tutorial directory, typically located here:

<INSTALL\_DIR>\SpeedXP\Samples\SystemSI\Parallel Bus Analysis\Tutorial

*Note:* Instead of updating the files in the sample directory, it is recommended that you copy these files to your working directory and work on them.

This document does not go into detail on theory. Please refer to **Application Notes** for additional documentation.

Contact Cadence support at <u>si-support@cadence.com</u> for more focused application assistance.

The example used in this tutorial is a simple DDR3 memory bus, including controller, PCB and DRAM devices.

Key topics that will be covered can be grouped into 3 broad categories: model creation, design entry, and simulation.

Each chapter is written to be a standalone module for users to follow for specific task-focused activity.

Please feedback any problems or issues found with this document to Cadence support.

## 2 Quick Start

## 2.1 Overview

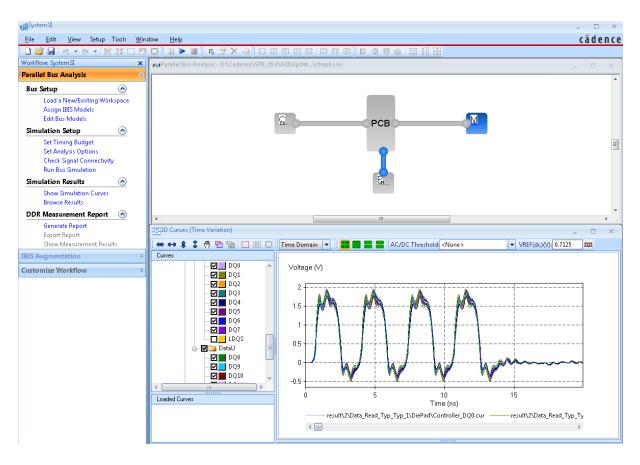

As an introduction to **Parallel Bus Analysis**, we will start by looking at one of the templates that are installed with the tool. This will allow us to look at the GUI, design entry commands, simulation setup and data presentation windows.

## 2.2 Open a Template

- 1. Launch SystemSI.

- 2. To open a new workspace, select *File -- New*.

Alternatively, you can also click the **New** icon.

#### The Select Module window opens.

| Se | lect Module           | X         |

|----|-----------------------|-----------|

|    | Module Name           |           |

|    | Parallel Bus Analysis |           |

|    | Serial Link Analysis  |           |

|    | Testbench             |           |

|    |                       |           |

|    |                       |           |

|    |                       |           |

|    |                       |           |

|    |                       | OK Cancel |

- 3. Select Parallel Bus Analysis.

- 4. Click **OK**.

- The Choose License Suites window appears.

- 5. Select the license and click **Close**.

- The New Workspace window opens.

- 6. Select Create by Template.

- 7. Select data\_bus\_welem\_vrm.

| New Workspace O Create by setting O Create by template Ter                                                  | nplate Path: [5\ASI\BASE\speedxp\library\template                                                                                                                                     | ×<br>e\SystemSI\ParallelBus |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Name                                                                                                        | Path                                                                                                                                                                                  | Description                 |

| addr_bus_sparam_4mem<br>data_bus_sparam_2mem<br>data_bus_welem_2rank<br>data_bus_welem_yrm<br>pba_simple_em | D:\Cadence\SPB_16.6\ASI\BASE\spee<br>D:\Cadence\SPB_16.6\ASI\BASE\spee<br>D:\Cadence\SPB_16.6\ASI\BASE\spee<br>D:\Cadence\SPB_16.6\ASI\BASE\spee<br>D:\Cadence\SPB_16.6\ASI\BASE\spee |                             |

| •                                                                                                           | 111                                                                                                                                                                                   |                             |

| Name:<br>Location: D:\sipbatut                                                                              |                                                                                                                                                                                       |                             |

|                                                                                                             | E                                                                                                                                                                                     | OK Cancel                   |

- 8. Enter a Name for the project. For this tutorial, enter the name as *mysipba*.

- 9. Enter a **Locatio**n.

|       | A directory with the workspace name is created in the location specified.                                                                                                                                             |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOTE! | This directory contains the workspace file, <i>mysipba.ssix</i> , as well as all of the models for the memory controller, memory device and other bus blocks that are available in the single device template folder. |

10. Click **OK**.

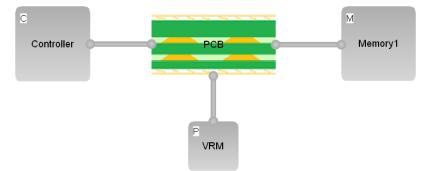

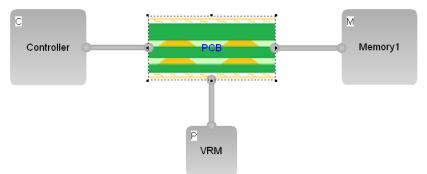

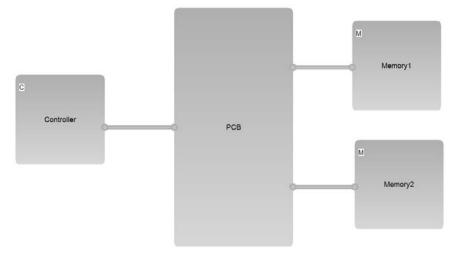

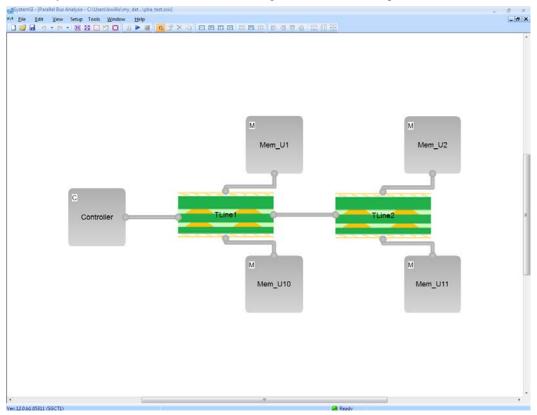

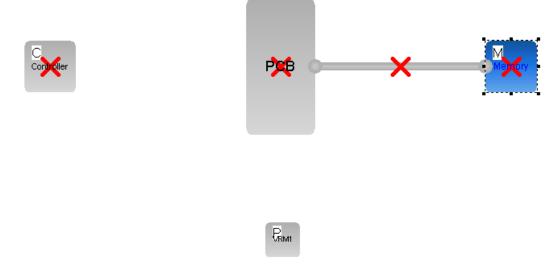

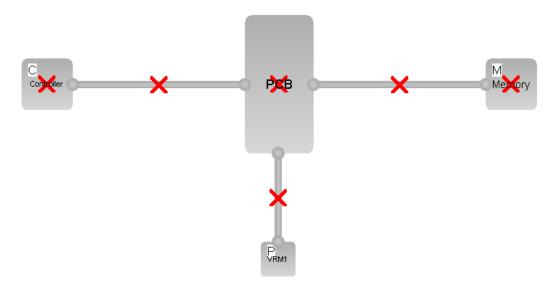

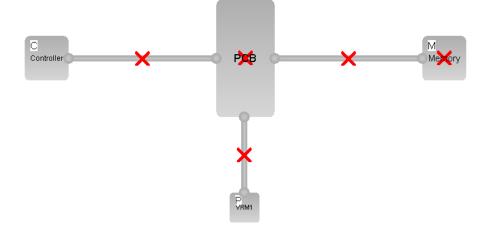

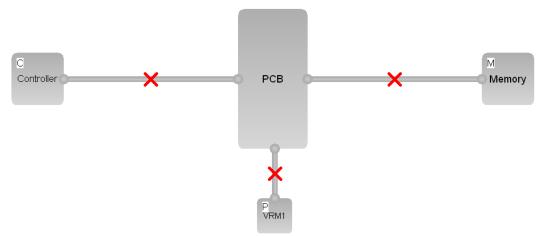

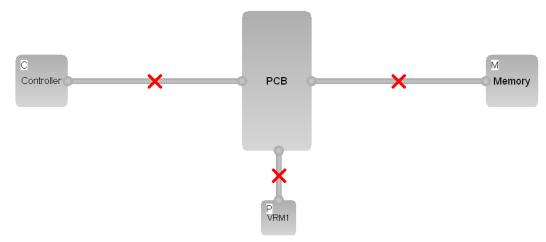

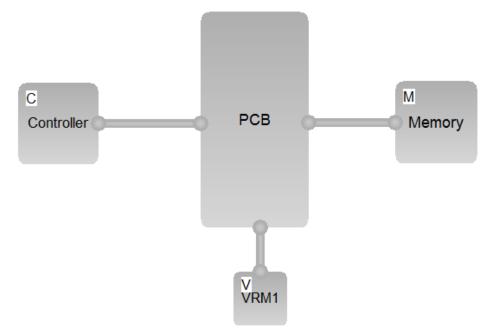

The Block diagram is created.

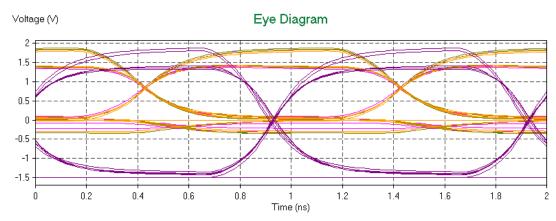

This is a pre-constructed, ready to simulate template, consisting of a controller and a single memory device. IBIS models are defined, edited, and linked to the devices. The PCB interconnects are coupled transmission line models, consisting of HSPICE W-element components. There is also a Voltage Regulator Module (VRM) block that has power supply explicitly defined. This is required for simulations including non-ideal power (i.e. no "ideal power" assumption at the IO models).

## 2.3 Editing Components

Irrespective of the method used to create the design, if required, you can edit the blocks as well as the connections. Editing a block and connection in the system is done by double-clicking the block.

### 2.3.1 PCB Block

1. Double-click the **PCB** component.

The **Property** dialog box opens. The left side of this dialog defines the **Connections** to this component, using Sigrity model-connection protocol (MCP).

| Conn. Port    | Connect To | Block Name | Conn. Port |               | subckt pcb_traces                                                                                                                                                                                                 |

|---------------|------------|------------|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to_Controller |            | Controller | to_PCB     | Edit Layout L | + a2 b2 c2 d2 e2 f2 g2 h2 i2 j2 k2 ref                                                                                                                                                                            |

| to_Memory1    |            | Memory1    | to_PCB     | Edit Layout L | + pwr_vrm pwr_controller pwr_mem<br>+ gnd vrm                                                                                                                                                                     |

| to_vrm        |            | VRM        | vrm_power  | Edit Layout L | + grid_vrin                                                                                                                                                                                                       |

|               |            |            |            |               | * [MCP Begin]<br>* [Connection] to_Controller<br>* [Connection] to_Controller<br>* [Cover Nets]<br>* Lumped(36) pwr_controller VDDQ<br>* [Ground Nets]<br>* Lumped(38) ref V5SQ<br>* [Signal Nets]<br>* 62 e1 DQ4 |

|               |            |            |            |               |                                                                                                                                                                                                                   |

| 4             |            | 111        |            | -             | Launch MCP Header Editor TLine Editor Import Edit Sub-circuit Definition                                                                                                                                          |

2. Click the Green **Connect To** wires icons.

The MCP connectivity between these components, with specific pin to pin mapping, is shown.

| Block Name: PCB                  | Block Name: Memory1                      |   |

|----------------------------------|------------------------------------------|---|

| Conn. Port: to_Memory1           | Conn. Port: to_PCB                       |   |

| PinName / CktNodeName / NetName  | PinName / CktNodeName / NetName          |   |

| A1 / pwr_mem / VDDQ              | A1 / A1 / VDDQ                           |   |

| = B1 / ref / VSSQ                | B1 / B1 / V55Q                           |   |

| E3/a2/DQ0                        | E3 / E3 / DQ0                            |   |

| F2 / c2 / DQ2                    | F2 / F2 / DQ2                            |   |

| F3 / j2 / LDQ5                   | F3 / F3 / LDQS                           |   |

| F7 / b2 / DQ1                    | F7 / F7 / DQ1                            |   |

| F8 / d2 / DQ3                    | F8 / F8 / DQ3                            |   |

| G2 / g2 / DQ6                    | G2 / G2 / DQ6                            |   |

| G3 / k2 / LDQ5#                  | G3 / G3 / LDQ5#                          |   |

| H3 / e2 / DQ4                    | H3 / H3 / DQ4                            |   |

| 🚽 H7 / h2 / DQ7                  | н7 / H7 / DQ7                            | - |

| Y                                | Auto Connect Auto net property overwrite |   |

|                                  |                                          |   |

| Connection Connection definition |                                          |   |

3. Click **Cancel** to exit this MCP dialog without making changes.

The right side of the Property dialog has model or circuit netlist definition for the component. This SPICE netlist file can be swapped for an alternative file, or edited in a text editor.

The W-element description for the PCB traces in this file can be viewed by scrolling down as shown in the following figure.

| File Name: D:\sipbatut\aa\pcb_traces.sp Sub-circuit Name: pcb_traces         | • |

|------------------------------------------------------------------------------|---|

| .Model pcb_traces_pcb_traces_Wmodel1 W MODELTYPE=RLGC N=11                   |   |

| +Lo=                                                                         |   |

| + 3.39692013e-007                                                            |   |

| + 2.50220882e-008 3.38937451e-007                                            |   |

| + 1.97017452e-009 2.49627545e-008 3.38932785e-007                            |   |

| + 1.55167741e-010 1.96550152e-009 2.49623871e-008 3.38932756e-007            |   |

| + 1.22207723e-011 1.54799703e-010 1.96547258e-009 2.49623848e-008 3.38932756 |   |

| + 9.62489215e-013 1.21917863e-011 1.54797424e-010 1.96547240e-009 2.49623846 | - |

| + 7.58043534e-014 9.60207123e-013 1.21916079e-011 1.54797423e-010 1.96547257 |   |

| + 5.65875370e-015 7.56257868e-014 9.60206739e-013 1.21917810e-011 1.54799638 |   |

| + 0.00000000e+000 5.65837925e-015 7.57997024e-014 9.62423166e-013 1.2219951  |   |

| + 0.00000000e+000 0.0000000e+000 0.0000000e+000 1.25958835e-014 1.616929     |   |

| + 0.00000000e+000 0.00000000e+000 0.00000000e+000 0.00000000e+000 1.26323    |   |

| + Co=                                                                        |   |

| + 1.24293483e-010                                                            | • |

|                                                                              |   |

| Launch MCP Header Editor TLine Editor Import Edit Sub-circuit Definition     | ] |

4. In case you need to edit the model or circuit netlist definition, click the **Edit Sub-circuit Definition** button.

The file opens in editable mode in the Sub-circuit Definition Editor tab. You can make the required modifications to the file and click OK to save the changes.

- 5. For this design example, exit the Sub-circuit Definition Editor tab without making changes.

- 6. If required, you can add or modify the MCP header by selecting the Launch MCP Header File button.

| Sub-circuit         |   | Туре                |          | Conn. Port                |   |   | Туре           |

|---------------------|---|---------------------|----------|---------------------------|---|---|----------------|

| pcb_traces          |   |                     |          | to_Memory1                |   |   |                |

|                     |   | 1                   |          | to_vrm<br>to_Controller   |   |   |                |

| Ckt Node            |   |                     | ⊫        |                           |   |   |                |

| Signal Net(s)<br>a1 |   | -> Signal Net       |          | Name / CktNodeName / NetN | X | Y | Thru Conn. Por |

| a2                  |   |                     | Θ        | Signal Net(s)             |   |   |                |

| 62<br>b1            |   |                     |          | E3 / a2 / DQ0             |   |   | to_Controlle   |

| b1<br>b2            |   | -> Power Net        |          | E7 / i2 / LDM             |   |   |                |

| c1                  | = |                     |          | F2 / c2 / DQ2             |   |   | to_Controlle   |

| c2                  | - |                     | 5        | F3 / j2 / LDQS            |   |   | to_Controlle   |

| d1                  |   | -> Ground Net       |          | F7 / b2 / DQ1             |   |   | to_Controlle   |

| d2                  |   |                     | <u> </u> | F8 / d2 / DQ3             |   |   | to_Controlle   |

| e1                  |   | Select ckt node(s)  |          | G2 / g2 / DQ6             |   |   | to_Controlle   |

| e2                  |   | and add it(them) to |          | G3 / k2 / LDQ5#           |   |   | to_Controlle   |

| 6L<br>f1            |   | the selected Conn.  |          | H3 / e2 / DQ4             |   |   | to_Controlle   |

| f2                  |   | Port.               |          | H7 / h2 / DQ7             |   |   | to_Controlle   |

| q1                  |   |                     |          | H8 / f2 / DQ5             |   |   | to_Controlle   |

| g2                  |   |                     |          | Power Net(s)              |   |   |                |

| h1                  |   |                     |          | A1 / pwr_mem / VDDQ       |   |   | to_Controll.   |

| h2                  |   |                     |          | Ground Net(s)             |   |   |                |

| i1                  |   |                     |          | B1 / ref / VSSQ           |   |   | to_Controll.   |

| i2                  |   |                     |          |                           |   |   |                |

| <b>41</b>           |   |                     |          |                           |   |   |                |

**NOTE!** If the .sp or the .ckt file does not have the MCP header, you need to add the same by editing the MCP header. By default, models generated by Sigrity tools (.sp or.ckt), contains the MCP header.

7. Exit the MCP Header Editor without making any modifications.

**NOTE:** The **TLine Editor** button is used to define the properties of the transmission line block (PCB). Use the **Import** button to import the properties of the Tline block already defined in other project files. To know more about the usage of these buttons, see *Pre-Layout Transmission Line Modeling AppNote:SystemSI*.

#### 2.3.2 Controller / Memory Block

1. Double-click the **Controller** or **Memory** component.

|            | roller     |            |               | Tx OnDie Parasitics Package Parasitics Ignore VT Curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conn. Port | Connect To | Block Name | Conn. Port    | IBIS File: D:\ASI166\1664\SSI_PBA\pba1\ssi_pba_{ d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| to_PC8     |            | PCB        | to_Controller | subdxt Controller         +2       3       15       17       18       19       20       21       22       23       33       42         +43       51       52       62       64       67       69       75       77       80       82       85         +87       94       96       99       101       104       106       111       113       116       118         +1       36       5       38       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       *       * |

The **Property** dialog box that opens is similar to the one for the PCB, except for the editing function. Instead of a simple text editor, there is a **Load IBIS...** button.

2. Click the **Load IBIS...** button, and view the IBIS model definition for this Controller component.

In this window, the IBIS models maybe specified, and the **Pin Mapping** and **Bus Definitions** for the model can be viewed and defined. Changes made in this window will update the IBIS file.

| oad IBIS                                                         |                         |         |           |             |             |                    |                    | - 🗆 ×     |

|------------------------------------------------------------------|-------------------------|---------|-----------|-------------|-------------|--------------------|--------------------|-----------|

| D:\sipbatut\                                                     | \mysipba\ssi_pba_ex.ibs |         |           |             | Comp        | onent : Controller |                    | Edit IBIS |

| Pin Mapping Bus Definition Explicit IO Power and Ground Terminal |                         |         |           |             |             |                    | d Ground Terminals |           |

| Pin                                                              | Pulldown                | Pullup  | GND Clamp | Power Clamp | Signal Name | Model Name         | Bus Group          |           |

| 1                                                                |                         | PWRBUS1 |           |             | VDD         | POWER              |                    | =         |

| 10                                                               | GNDBUS1                 | PWRBUS1 | GNDBUS1   | PWRBUS1     | RESET       | DDR3_DQ34_N        |                    |           |

| 100                                                              | GNDBU52                 |         |           |             | ¥55Q        | GND                |                    |           |

| 101                                                              | GNDBUS2                 | PWRBUS2 | GNDBU52   | PWRBUS2     | DQ9         | DDR3_DQ34_N        | DataU              |           |

| 102                                                              |                         | PWRBUS2 |           |             | VDDQ        | POWER              |                    |           |

| 103                                                              |                         | PWRBUS2 |           |             | VDDQ        | POWER              |                    |           |

| 104                                                              | GNDBUS2                 | PWRBUS2 | GNDBU52   | PWRBUS2     | UDQS        | DDR3_DQS34         | Timing Ref         |           |

| 105                                                              | GNDBUS2                 |         |           |             | ¥55Q        | GND                |                    |           |

| 106                                                              | GNDBUS2                 | PWRBUS2 | GNDBU52   | PWRBUS2     | UDQ5#       | DDR3_DQS34         | Timing Ref         |           |

| 107                                                              |                         | PWRBUS2 |           |             | VDDQ        | POWER              |                    |           |

| 108                                                              |                         | PWRBUS1 |           |             | VDD         | POWER              |                    |           |

| 109                                                              | GNDBUS1                 |         |           |             | VSS         | GND                |                    |           |

| 11                                                               |                         |         |           |             | DNU         | NC                 |                    |           |

| Filter                                                           |                         |         |           |             |             |                    | ОК                 | Cancel    |

The MCPs of the Controller and Memory blocks are generated by SystemSI based on the bus definition, Pin Mapping, and setup of the **Load IBIS** GUI. These are not editable.

To know more about the MCP generation process, see Rules for Generating MCPs.

3. Click **Cancel** to exit without making changes.

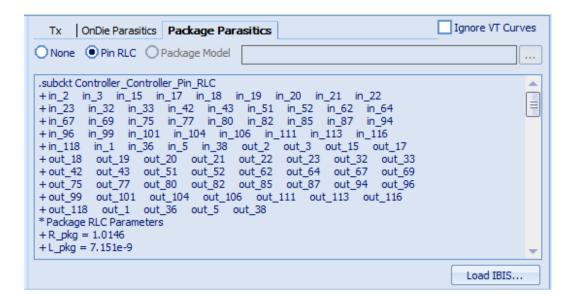

In the **Property** dialog, the OnDie Parasitics and Package Parasitics tabs can be used specify the **Die** and **Package** models, respectively. These can be separate model files, like a PKG file, or simply the RLC package parasitics that are already included in the IBIS model.

4. To view the Pin model in the IBIS file, click the **Package Parasitics** tab and select **Pin RLC**.

|      | For Parallel Bus Analysis, the Ignore VT Curves option is not selected by         |

|------|-----------------------------------------------------------------------------------|

| NOTE | default. This is to ensure that during analysis, simulator takes into account the |

|      | non-liner behavior of the drivers by reading the VT data.                         |

#### 2.3.2.1 MCP Generation for Controller and Memory IBIS Blocks

This section details the rules or the guidelines followed by SystemSI for generating MCPs.

In the Load IBIS dialog box, if the Explicit IO Power and Ground Terminals option is not checked, the Ckt Node, Net, and Pin in the MCP are determined by the Pin Mapping section of the IBIS component.

| Block Nam | e:        | Controller                      |   |

|-----------|-----------|---------------------------------|---|

| Conn. Por | t:        | to_PCB                          |   |

| A PinNa   | ame / Ckt | NodeName / NetName (Sort By Ck. | / |

|           | 64 / 64   | / DQ6                           |   |

|           | 67   67   | / DQ7                           |   |

|           | 69   69   | / DQ5                           |   |

|           | 75   75   | /LDQS#                          |   |

|           | 77   77   | / LDQS                          |   |

|           | 80 / 80   |                                 |   |

| _         | 82   82   |                                 |   |

| =         | 85 / 85   |                                 |   |

|           | 87   87   |                                 |   |

|           |           | ected Signal Net(s)             |   |

|           |           | 2 / CLK1N                       |   |

|           | •         | 3 / CLK1P                       |   |

|           |           | 15 / 47                         |   |

|           |           | 17 / A2                         |   |

|           |           | 18 / A6<br>19 / A5              |   |

|           |           | 19 / A5<br>20 / A1              |   |

|           | •         | 20 / A1<br>21 / A3              |   |

|           | •         | 22 / A4                         |   |

|           |           | 23 / A0                         |   |

|           |           | 20770                           |   |

- The values in the **Ckt Node** and **Pin** columns are the same, and are read from the **Pin** column in the **Pin Mapping** section of the Load IBIS dialog box.

- The values in the Net column of the MCP Editor are same as the values in the Signal Name column in the Pin Mapping section of the Load IBIS dialog box.

- 2. If the Load IBIS dialog box has the **Explicit IO Power and Ground Terminals** option checked, in the generated MCP, each signal has its corresponding power and ground as shown in the following figure.

| Copp | Port:              | to PCB                               |

|------|--------------------|--------------------------------------|

|      | , Port,            | 0,70                                 |

| PinN | lame / CktNod      | leName / NetName (Sort By Ckt N 🔽    |

|      | Unconnecte         | ed Signal Net(s)                     |

|      | 15 / A7            | •                                    |

|      | 18 / A6            | •                                    |

|      | 19 / A5            |                                      |

|      | 22 / A4<br>21 / A3 |                                      |

|      | 21 / A3<br>17 / A2 | •                                    |

|      | 20 / A1            |                                      |

|      | 23 / A0            | •                                    |

|      |                    | -                                    |

|      |                    |                                      |

|      |                    |                                      |

|      |                    | ed Power Net(s)                      |

|      |                    | ) / A7_VDD / VDD                     |

|      |                    | ) / A6_VDD / VDD<br>) / A5_VDD / VDD |

|      |                    | ) / A4_VDD / VDD                     |

|      |                    | / A3_VDD / VDD                       |

|      |                    | / A2_VDD / VDD                       |

|      | A1_VDD             | / A1_VDD / VDD                       |

|      | A0_VDD             | ) / A0_VDD / VDD                     |

|      |                    | ed Ground Net(s)                     |

|      |                    | / A7_VSS / VSS                       |

|      |                    | / A6_VSS / VSS                       |

|      |                    | / A5_VS5 / VS5<br>/ A4_VS5 / VS5     |

|      | _                  | / A4_VS5 / VS5<br>/ A3_VS5 / VS5     |

|      |                    | / A3_VS5 / VS5                       |

|      | _                  | / A1_VSS / VSS                       |

|      |                    | / A0_VSS / VSS                       |

The MCP is generated using following rules:

- In case of a regular signal, the **Ckt Node** value is same as the **Signal Name** in the **Pin Mapping** section

- For the corresponding power signals, the values in the **Ckt Node** and **Pin** columns are the same, and these are derived by combining the signal Net and power Net.

- Similarly, for the Ground of the signal, the **Ckt Node** and **Pin** values are the same, and these are derived from the signal Net and the ground Net.

You can click **Ckt Node** of the Controller/Memory block to sort the **Ckt Node** for easy connection.

The signal and its power and ground are grouped together for the Controller/Memory block in order to make the manual connecting easy.

| NOTE! | When Explicit IO Power and Ground Terminals are utilized, all the powers and grounds of the Controller/Memory must be connected in order to do the non-ideal power bus simulation. |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

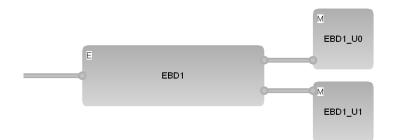

#### 2.3.3 EBD Block

While using SystemSI you can also import the Electrical Board Description (EBD) models that are as per the IBIS specification. EBD models are imported directly into SystemSI and automatically expanded out to include interconnect and referenced component blocks. EBD files are commonly used for modeling DIMMS.

**NOTE:** In SystemSI you cannot instantiate an EBD block along with a memory block. This is not supported.

#### 2.3.3.1 EBD File

When you associate an EBD model to an EBD block in SystemSI, the model information is displayed in the four tabs of the Load EBD dialog box.

#### IBIS Tab

This tab lists all the Memory blocks and Terminators listed as Reference Designators. To view the Pin Mapping of a memory block or a terminator, from the **Reference Designator** drop-down list, select the refdes of the component.

Note: A Terminator can have its own IBIS component; but all the Memory blocks must share the same component of the same ibis file.

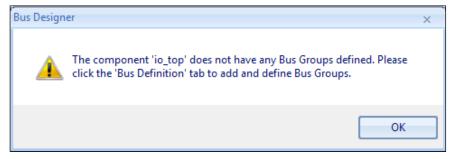

#### **Bus Definition**

This tab lists the Bus groups defined for the Memory component. If required, use this tab to add and define new bus groups.

#### Power & GND net

The EBD model does not have the definitions for the Power and Ground nets. In order for the IBIS components to get the power supply from outside the EBD, each IBIS Power Pin must be linked to one EBD Power Pin that is connected to other blocks. The same is true for the IBIS Ground Pins.

| NOTE! | Only the IBIS Power and Ground Pins that are associated with the defined |

|-------|--------------------------------------------------------------------------|

|       | Bus signals are listed in the <b>Power &amp; GND net</b> tab.            |

#### Signal Net

The IBIS Pins are for the defined Bus signals of the Memory blocks. If a signal is defined in the EBD file, it's IBIS Pin and the EBD Pin will be listed together in the same row. All the EBD pins are listed in the MCP are use for the connection to the other blocks.

| RD Rin   | EBD Signal | Туре       | IBIS Pin   | IBIS File     | IBIS Component | IBIS Signal |  |  |

|----------|------------|------------|------------|---------------|----------------|-------------|--|--|

| 33       | DQ0        | Signal     | U0.87      | v69a bd stack | MT413512M4     |             |  |  |

|          | DO2        | Signal     | U0.85      |               | MT413512M4     |             |  |  |

| 12<br>13 | DQS        | Timing Ref | U0.77      |               | MT413512M4     |             |  |  |

| 7        | DQ1        | Signal     | U0.80      |               | MT413512M4     |             |  |  |

| 8        | DO3        | Signal     | U0.82      |               | MT413512M4     |             |  |  |

| 03       | DQS#       | Timing Ref | U0.75      |               | MT413512M4     |             |  |  |

| 33       | DQ0        | Signal     | U1.87      | v69a bd stack | MT413512M4     | DQ0         |  |  |

| 2        | DQ2        | Signal     | U1.85      | v69a_bd_stack | MT413512M4     | DQ2         |  |  |

| 3        | DQS        | Timing Ref | U1.77      | v69a_bd_stack | MT413512M4     | DQS         |  |  |

| .7       | DQ1        | Signal     | U1.80      | v69a_bd_stack | MT413512M4     | DQ1         |  |  |

| 8        | DQ3        | Signal     | U1.82      | v69a_bd_stack | MT41J512M4     | DQ3         |  |  |

| 3        | DQ5#       | Timing Ref | U1.75      | v69a_bd_stack | MT413512M4     | DQ5#        |  |  |

|          | Listed as  | Signals i  | n the MCP: | to_PCB,       |                |             |  |  |

#### 2.3.3.2 Using EBD Models in System SI

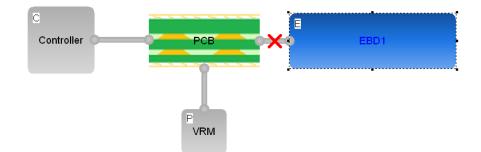

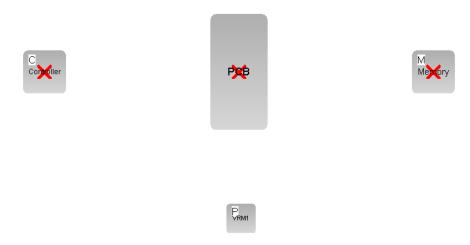

To import an EBD models in SystemSI, you first add an instance of EBD block on the schematic and then associate the EBD file with the EBD block.

To instantiate an EBD block:

1. Click the 💷 button.

*Note: This button is enabled only if you do not have a memory block instantiated on the canvas.*

- 2. Click on the canvas to add an instance of EBD component.

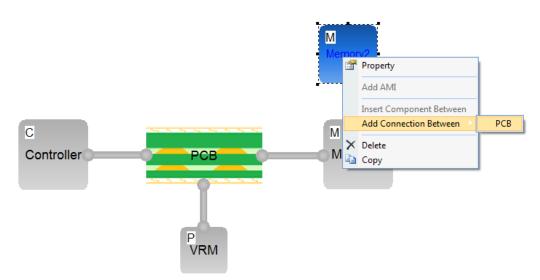

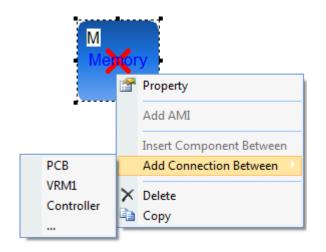

- 3. To connect EBD block to the PCB block, right-click on the EBD1 instance and from the pop-up menu choose **Add Connection Between PCB**.

- 4. To assign an EBD model to the EBD block, open the Property window for the EBD block.

- 5. Click the Load EBD... button

- 6. In the Load EBD dialog box, use the Browse (...) button to navigate to the .EBD file.

- As you load the EBD file, the IBIS, Bus Definition, Power & GND Net and Signal Net for the model can be viewed in the respective tab. If required you can modify these. Changes made in the IBIS and Bus Definition panels will update the IBIS files.

- 8. Click OK to close the Load EBD dialog box.

- 9. Click the Apply button to build the EBD model.

Depending of the EBD model, new Memory blocks are automatically added to the schematic.

## 2.3.4 S Parameter Block

#### 2.3.4.1 Add S Parameter Block

1. Click the Add S Parameter Block icon 🗊 on the tool bar, and click in the Layout window. The S Parameter block S1 is added.

| r 🖌 🚡 🖌  | 5 @ @ V @ @ @         |

|----------|-----------------------|

|          | Add S Parameter Block |

|          |                       |

| S        |                       |

|          |                       |

| ×        |                       |

| <b>~</b> |                       |

|          |                       |

|          |                       |

| <u>.</u> |                       |

2. Double-click the **S1** block.

The **Property** pane opens.

| roperty        |               |                     |   |    |        | -           |

|----------------|---------------|---------------------|---|----|--------|-------------|

| Block Name: S1 |               |                     |   |    |        |             |

| Conn. Port     | Connect To Bl | ock Name Conn. Port |   |    |        |             |

|                |               |                     |   |    |        |             |

|                |               |                     |   |    |        |             |

|                |               |                     |   |    |        |             |

|                |               |                     |   |    |        |             |

|                |               |                     |   |    |        |             |

|                |               |                     |   |    |        |             |

|                | 111           |                     | ▶ |    | Load S | Parameters. |

| onnection      |               |                     |   |    |        |             |

|                |               |                     |   | ОК | Cancel | Apply       |

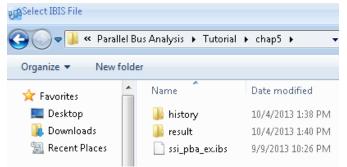

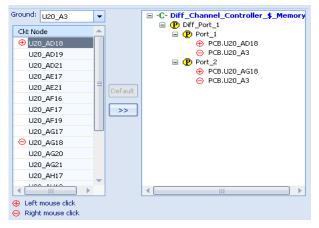

#### 2.3.4.2 Load S Parameter File

1. Click the Load S Parameters... button.

| Organize 🔻 New fol  | der                  |                              | =                     |

|---------------------|----------------------|------------------------------|-----------------------|

| ☆ Favorites         |                      | Date modified Type           | Size                  |

| Desktop             | bufferdelay          | 4/1/2013 3:56 PM File folde  | r                     |

| Downloads           | Chapter3_IBIS        | 12/19/2012 10:32 File folde  |                       |

| Recent Places       | history              | 5/2/2013 10:21 AM File folde |                       |

| 😪 My Site           | in result            | 4/8/2013 11:08 AM File folde |                       |

|                     | DDR2_s2k_sample1.bnp | 11/26/2012 1:38 AM BNP File  | 15,074                |

| 🔚 Libraries 📕       | tutorial_PCB1.bnp    | 11/26/2012 1:40 AM BNP File  | 3,256                 |

| Documents           |                      |                              |                       |

| J Music             |                      |                              |                       |

| Pictures            |                      |                              |                       |

| Videos              |                      |                              |                       |

| 🖳 Computer          |                      |                              |                       |

| 🚢 Local Disk (C:)   |                      |                              |                       |

| 👝 Local Disk (D:) 🖕 | •                    | III                          |                       |

|                     | name:                | ✓ S Parameter Fil            | e(*.bnp; *.s?p; *.: 🔻 |

The Load S Parameters window opens.

2. Load the S Parameter file (BNP or Touchstone) to the S Parameter block.

For this tutorial, load the **tutorial\_PCB1.bnp** file available at <install\_dir>/SpeedXP/Samples/SystemSI/Parallel Bus Analysis/Tutorial

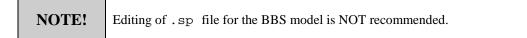

Once the selected S Parameter file is successfully loaded, . sp file is automatically generated and loaded to the block.

- The .sp filename is displayed in the File Name field.

- The S Parameter filename is displayed in the S Parameter File field.

| S Parameter File: | D:\Cadenc=\SPB_16.6\AS | (\Update4\SpeedXP\Sampl | es\System5 | View S Paramete | er           |

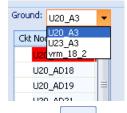

|-------------------|------------------------|-------------------------|------------|-----------------|--------------|

| .SUBCKT           | S1 tutorial PCB1 bnp   |                         |            |                 | *            |

| +                 | U20_AC8                |                         |            | ſ               |              |

| +                 | U20_A3                 |                         |            | Ì               |              |

| +                 | U20_AF16               |                         |            |                 |              |

| +                 | U20_AE17               |                         |            |                 |              |

| +                 | U20_AH17               |                         |            |                 |              |

| +                 | U20_AG17               |                         |            |                 |              |

| +                 | U20_AG18               |                         |            |                 |              |

| +                 | U20_AH18               |                         |            |                 |              |

| +                 | U20_AD18               |                         |            |                 |              |

| +                 | U20_AF19               |                         |            |                 |              |

| +                 | U20_AH19               |                         |            |                 |              |

| +                 | U20_AD19               |                         |            |                 |              |

| +                 | U20_AG20               |                         |            |                 |              |

| +                 | U20_AH20               |                         |            |                 | $\mathbf{T}$ |

| •                 | 111                    |                         |            | •               |              |

| Extract BBS Mod   | el Load BBS Model      | Launch MCP Header Edi   | tor Loa    | d S Parameters  |              |

- If the BNP file has the MCP information, the MCP section is automatically added to the .sp file for connection.

- In case the Touchstone or BNP files do not have the MCP information, you are expected to manually add the MCP through the MCP Editor.

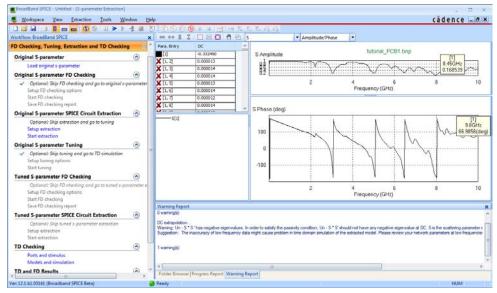

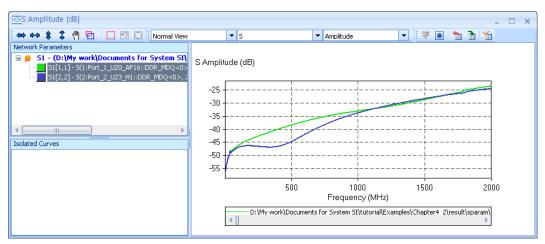

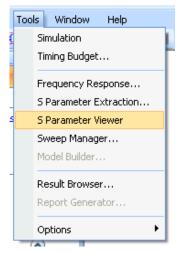

#### 2.3.4.3 Extract the BBS Model

To improve convergence and simulation performance, it is sometimes advantageous to convert the S-parameters into a Broadband Spice circuit model. This section covers the steps to generate a circuit model from the S-parameter model used in the previous section.

1. In the Property dialog box for the S-parameter block, click the Extract BBS Model... button.

The BroadbandSPICE application is launched.

2. Click the **FD Checking**, **Tuning**, **Extraction and TD Checking** workflow to check and tune the S Parameters.

For the application of BroadbandSPICE, refer to *BroadbandSPICE\_Tutorial.pdf* and *BroadbandSPICE\_UG.pdf*.

3. If the S Parameter checking result looks good to you, click **Setup extraction** in the workflow.

| riginal S-parameter                    | <ul> <li></li> </ul> |

|----------------------------------------|----------------------|

| Load original s-parameter              |                      |

| riginal S-parameter FD Checking        |                      |

| Optional: Skip FD checking and go to   | original s-parame    |

| Setup FD checking options              |                      |

| Start FD checking                      |                      |

| Save FD checking report                |                      |

| riginal S-parameter SPICE Circuit Ext  | raction 🔗            |

| Optional: Skip extraction and go to tu | ning                 |

| Setup extraction                       |                      |

| Start extraction                       |                      |

| riginal S-parameter Tuning             | $\odot$              |

| Optional: Skip tuning and go to TD sir | mulation             |

| Setup tuning options                   |                      |

| Start tuning                           |                      |

| uned S-parameter FD Checking           | <u></u>              |

| Optional: Skip FD checking and go to   | tuned s-paramet      |

| Setup FD checking options              |                      |

| Start FD checking                      |                      |

| Save FD checking report                |                      |

| uned S-parameter SPICE Circuit Extra   | ction 📀              |

| Optional: Skip tuned s-parameter extr  | raction              |

| Setup extraction                       |                      |

| Start extraction                       |                      |

| D Checking                             | ٢                    |

| Ports and stimulus                     |                      |

| Models and simulation                  |                      |

| D and FD Results                       | ٢                    |

| TD results                             |                      |

| FD results                             |                      |

The **Options** window opens.

| Options                                  |                                                                                                            |

|------------------------------------------|------------------------------------------------------------------------------------------------------------|

| General  File Manager Simulation (Basic) | Change the 'Extraction settings' options in BroadBand SPICE                                                |

| General<br>Report template               | Highlight Error                                                                                            |

| Settings 📀                               | Highlight Errors Greater Than : 0.02                                                                       |

| Extraction settings<br>Checking settings | Extraction Mode                                                                                            |

| Tuning settings                          | Passivity mode     Maximum number of iterations for passivity enforcement:     200     Precision mode      |

|                                          | BBS Circuit                                                                                                |

|                                          | HSPICE Compatible     General SPICE Compatible                                                             |

|                                          | File Name : tutorial_PCB1_BBSdkt.txt                                                                       |

|                                          | S-parameter of BBS Circuit                                                                                 |

|                                          | Export      Touchstone Format     BNP Format     File Name : [utorial_PCB1_BBSckt_sp.s39p                  |

|                                          | Model Order Reduction                                                                                      |

|                                          | Ignore off-diagonal S parameters that are less than: Don't use reduction on these ports: Preserved Port(s) |

|                                          | Reduce upper frequency limit: 10 GHz V                                                                     |

|                                          | MCP File                                                                                                   |

|                                          | File Name :                                                                                                |

|                                          | Default Apply OK Cancel                                                                                    |

- 4. Set up the extraction settings as desired, and click OK to save your settings and to close the Options window.

- 5. Click **Start extraction** in the workflow to extract the BBS model.

If the BBS model extraction is successful, a .txt file is automatically generated in the folder that has the S-parameter (.bnp) file.

You can now load the generated BBS Model in SystemSI.

- 6. To load the generated BBS model **tutorial\_PCB1\_BBSckt.txt**, from the SystemSI GUI, click the **Load BBS Model...** button.

- 7. Select the circuit file and click Open.

| Load BBS Model                                                                                              |                |                              |                         |                     | ×              |

|-------------------------------------------------------------------------------------------------------------|----------------|------------------------------|-------------------------|---------------------|----------------|

| 🕤 🌍 – 🕌 « Tuto                                                                                              | rial I         | BBSResult_tutorial_PCB1      | <b>▼</b> 4 <sub>3</sub> | Search BBSResult_tu | ıtorial_PCB1 🔎 |

| Organize 🔻 New                                                                                              | folde          |                              |                         | :=                  |                |

| 🔆 Favorites                                                                                                 | •              | Name                         | Date modified           | Туре                | Size           |

| 🧮 Desktop                                                                                                   |                | 鷆 temp                       | 4/11/2013 10:59 AM      | File folder         |                |

| 〕 Downloads                                                                                                 |                | tutorial_PCB1_BBSckt.txt     | 4/11/2013 11:24 AM      | Text Document       | 8,415 K        |

| 🔛 Recent Places                                                                                             |                | tutorial_PCB1_BBSckt_2.txt   | 4/11/2013 11:24 AM      | Text Document       | 6,169 K        |

| 🧟 My Site                                                                                                   |                | tutorial_PCB1_for_RFM.txt    | 4/11/2013 11:24 AM      | Text Document       | 4 K            |

|                                                                                                             | -              | tutorial_PCB1_GSPICE.txt     | 4/11/2013 11:24 AM      | Text Document       | 44,706 K       |

| <ul> <li>☐ Libraries</li> <li>☐ Documents</li> <li>J Music</li> <li>☐ Pictures</li> <li>☑ Videos</li> </ul> |                |                              |                         |                     |                |

| 🖳 Computer                                                                                                  |                |                              |                         |                     |                |

| 🚢 Local Disk (C:)                                                                                           |                |                              |                         |                     |                |

| 👝 Local Disk (D:)                                                                                           | Ŧ              | •                            |                         |                     | •              |

| F                                                                                                           | ile <u>n</u> a | me: tutorial_PCB1_BBSckt.txt | ▼ BBS                   | Model File(*.txt)   | ▼<br>Cancel    |

Once the **BBS model is s**uccessfully loaded, an .sp file is **automatically generated** and loaded to the block.

- The .sp file is displayed in the File Name field

- The BBS model .txt file is displayed in the BBS Model File field

|     |                                                          |  | utorial\BBSRe Go To S | arameter |

|-----|----------------------------------------------------------|--|-----------------------|----------|

| CKT | S1_tutorial_PCB1_bnp                                     |  |                       |          |

|     | U20_AC8                                                  |  |                       | [        |

|     | U20_A3                                                   |  |                       | Ŀ        |

|     | U20_AF16                                                 |  |                       |          |

|     | U20_AE17                                                 |  |                       |          |

|     | U20_AH17                                                 |  |                       |          |

|     | U20 AG17                                                 |  |                       |          |

|     | U20_AG18                                                 |  |                       |          |

|     | U20 AH18                                                 |  |                       |          |

|     | U20 AD 18                                                |  |                       |          |

|     | U20 AF 19                                                |  |                       |          |

|     | U20 AH19                                                 |  |                       |          |

|     | U20 AD 19                                                |  |                       |          |

|     |                                                          |  |                       |          |

|     |                                                          |  |                       |          |

|     | U20_AG20                                                 |  |                       |          |

|     | U20_AG20<br>U20_AH20                                     |  |                       |          |

|     | U20_AG20<br>U20_AH20<br>U20_AH21                         |  |                       |          |

|     | U20_AG20<br>U20_AH20                                     |  |                       |          |

|     | U20_AG20<br>U20_AH20<br>U20_AH21<br>U20_AH21<br>U20_AE21 |  |                       |          |

#### 2.3.4.4 Load the BBS Model

If you have the BBS models for the selected S Parameters, click the **Load BBS Model...** button to directly load the BBS .txt file.

Please refer to Step 6 in Section 2.3.4.3 Extract the BBS Model for details.

If the loaded BBS model does not match the original S Parameters, an error message will be issued.

| SystemSI |                                                                                                           | × |

|----------|-----------------------------------------------------------------------------------------------------------|---|

| Â        | The loaded BBS model "DDR2_s2k_sample1_GSPICE.txt" does not match the original S Parameter model "Spara". |   |

|          | ОК                                                                                                        |   |

#### 2.3.4.5 Switch the Models

1. Click the Go To S Parameters button to switch to the original S Parameters model.

| File Name:       C:\Cadence\SPB_16.6\ASI\Base\SpeedXP\Samples\Sys       Sub-circuit Name:       S1_tutorial_                                                                                                                                                                                                  | PCB1_bnp                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| BBS Model File: C:\Cadence\SPB_16.6\ASI\Base\SpeedXP\Samples\SystemSI\Parallel Bus Analysis\Tutoria                                                                                                                                                                                                           | al\BBSRe Go To S Parameters |

| SUBCKT     S1_tutorial_PCB1_bnp       +     U20_AC8       +     U20_A7       +     U20_AF16       +     U20_AF17       +     U20_AG17       +     U20_AG18       +     U20_AF19       +     U20_AF19       +     U20_AD19       +     U20_AG20       +     U20_AH21       +     U20_AH21       +     U20_AH22 |                             |

| <b>↓</b>                                                                                                                                                                                                                                                                                                      |                             |

| Load BBS Model                                                                                                                                                                                                                                                                                                | Edit Sub-circuit Definition |

2. Click the Go To BBS button to switch back to the BBS model:

| File Name:   | C:\Cadence\SPB_16.6\ASI\Base\Speed   | XP\Samples\Sys Sub-circuit Name: S1_tutorial_PCB1_bnp 💌                                  |

|--------------|--------------------------------------|------------------------------------------------------------------------------------------|

| S Paramete   | r File: C:\Cadence\SPB_16.6\ASI\Base | <pre>SpeedXP\Samples\SystemSI\Parallel Bus Analysis\Tutorial\tutorial_PC</pre> Go To BBS |

| .SUBCKT<br>+ | S1_tutorial_PCB1_bnp<br>U20_AC8      |                                                                                          |

| +            | U20_A3                               |                                                                                          |

| +<br>+       | U20_AF16<br>U20_AE17                 |                                                                                          |

| +++          | U20_AH17<br>U20_AG17                 |                                                                                          |

| +++          | U20_AG18<br>U20_AH18                 |                                                                                          |

| ++           | U20_AD18<br>U20_AF19                 |                                                                                          |

| +++          | U20_AH19<br>U20_AD19                 |                                                                                          |

| +++          | U20_AG20<br>U20_AH20                 |                                                                                          |

| +            | U20_AH21                             |                                                                                          |

| +<br>+       | U20_AE21<br>U20_AH22                 |                                                                                          |

| +            | U20_AD21                             | <b>*</b>                                                                                 |

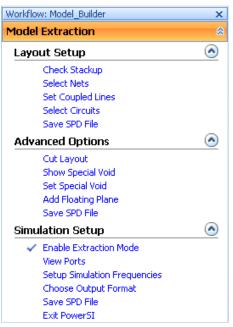

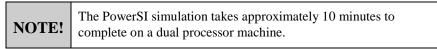

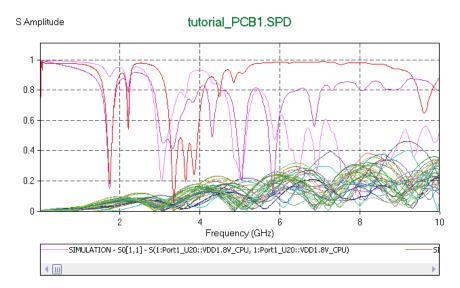

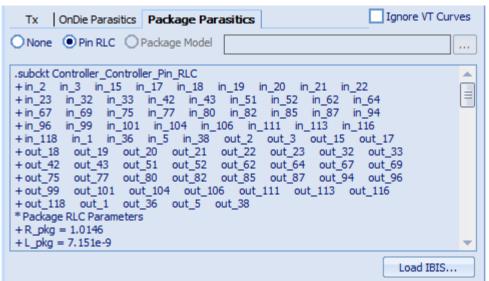

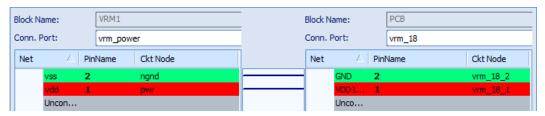

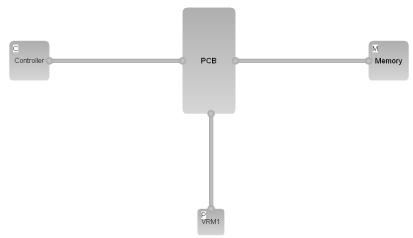

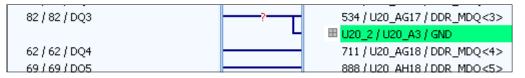

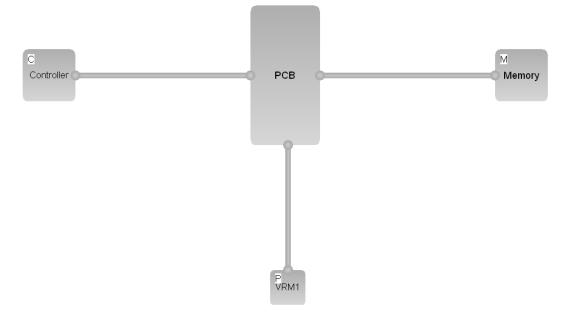

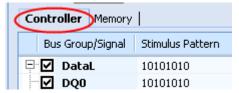

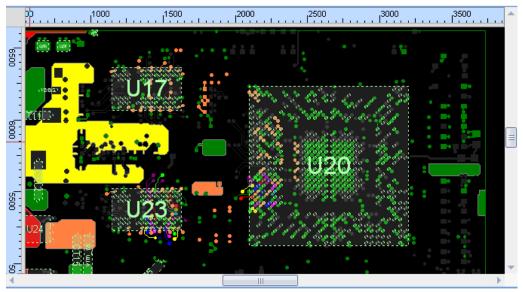

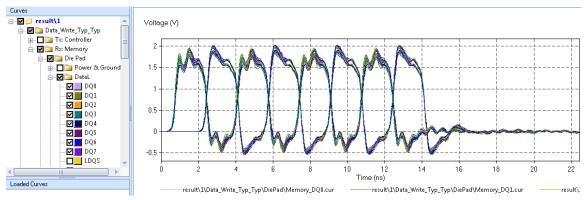

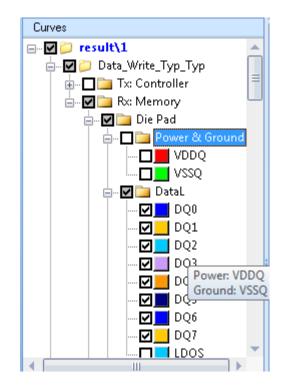

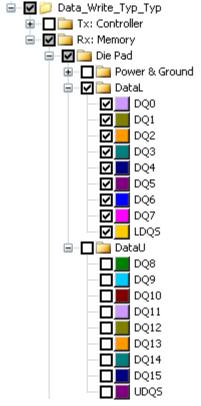

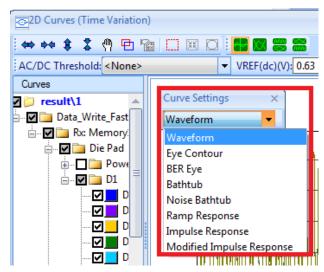

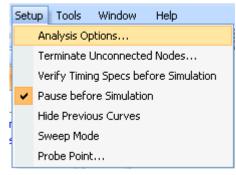

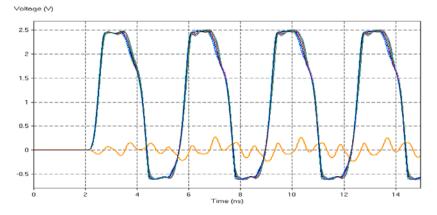

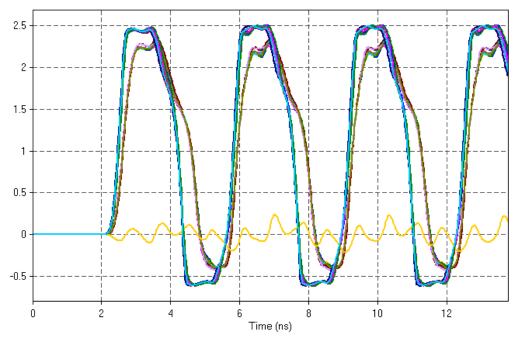

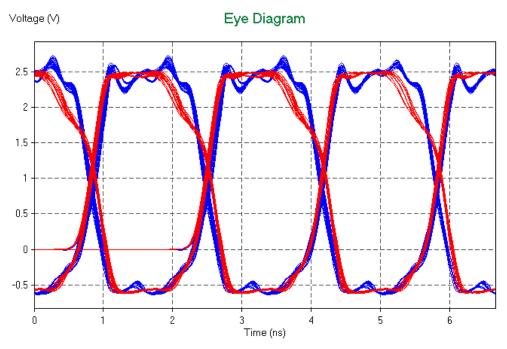

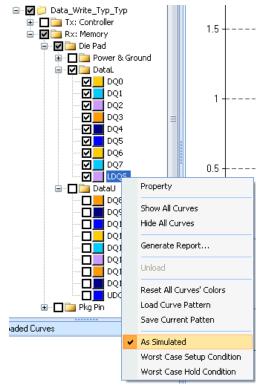

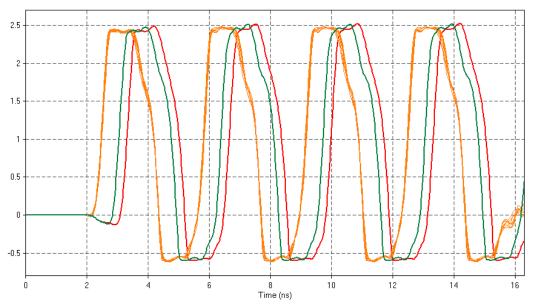

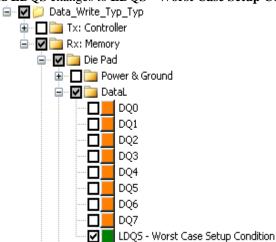

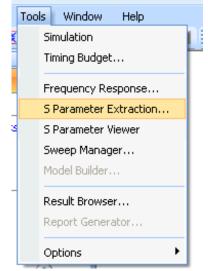

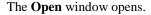

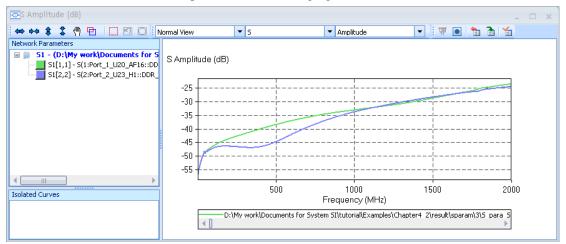

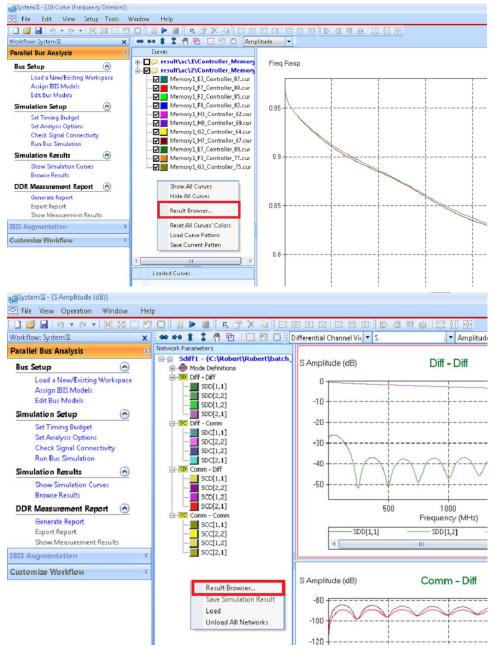

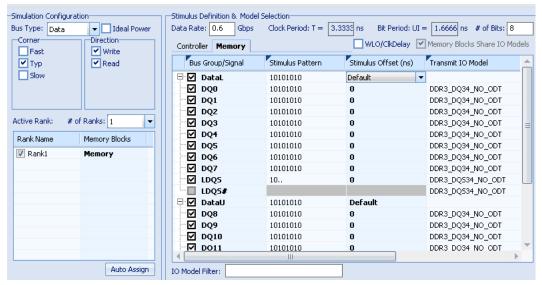

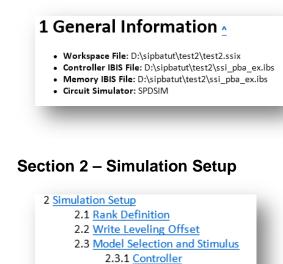

| Extract BB   | S Model                              | Load S Parameters Edit Sub-circuit Definition                                            |