# cādence<sup>®</sup>

## General\_SI\_Simulation\_Tutorial\_1

Product Version 16.6 July 2014 Legal

© 2014 Cadence Design Systems, Inc. All rights reserved. Printed in the United States of America.

Cadence Design Systems, Inc. (Cadence), 2655 Seely Ave., San Jose, CA 95134, USA.

Trademarks: Trademarks and service marks of Cadence Design Systems, Inc. (Cadence) contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence's trademarks, contact the corporate legal department at the address shown above or call 1-800-862-4522.

All other trademarks are the property of their respective holders.

Restricted Print Permission: This publication is protected by copyright and any unauthorized use of this publication may violate copyright, trademark, and other laws. Except as specified in this permission statement, this publication may not be copied, reproduced, modified, published, uploaded, posted, transmitted, or distributed in any way, without prior written permission from Cadence. This statement grants you permission to print one (1) hard copy of this publication subject to the following conditions:

1. The publication may be used solely for personal, informational, and noncommercial purposes;

2. The publication may not be modified in any way;

3. Any copy of the publication or portion thereof must include all original copyright, trademark, and other proprietary notices and this permission statement; and

4. Cadence reserves the right to revoke this authorization at any time, and any such use shall be discontinued immediately upon written notice from Cadence.

Disclaimer: Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. The information contained herein is the proprietary and confidential information of Cadence or its licensors, and is supplied subject to, and may be used only by Cadence's customer in accordance with, a written agreement between Cadence and its customer. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights, nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.

Restricted Rights: Use, duplication, or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successor.

## Contents

| 1                                           | 4  |

|---------------------------------------------|----|

| Introduction                                | 4  |

| Overview                                    | 4  |

| Tutorial Summary                            | 4  |

| 2                                           | 8  |

| Layout Setup                                | 8  |

| 3                                           | 10 |

| Simulation Setup                            | 10 |

| Enabling Simulation Nets                    | 10 |

| Assigning DC Voltage                        | 13 |

| Assigning Component Models                  | 13 |

| Assigning IBIS Model to IC Component U0     | 14 |

| Assigning IBIS Model to IC Component U1     | 19 |

| Copying IBIS Model to U2, U3 and U4 from U1 | 22 |

| Defining Passive Component Value            | 22 |

| SI Simulation Options Setup                 | 23 |

| General SI Options                          | 24 |

| U0 Parameters Setup                         | 25 |

| U1 Parameters Setup                         | 26 |

| U2 Parameters Setup                         |    |

| U3 Parameters Setup                         | 27 |

| U4 Parameters Setup                         | 28 |

| Probes Setup                                | 28 |

| Saving File                                 | 28 |

| 4                                           | 30 |

| Simulation and Results                      | 30 |

|                                             |    |

## Introduction

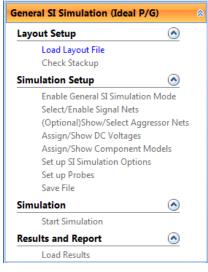

This tutorial introduces how to perform simulation with SPEED2000 General SI Simulation (Ideal P/G) workflow.

### **Overview**

The newly introduced SPEED2000 **General SI Simulation (Ideal P/G)** workflow is for general purpose signal integrity simulations without considering the non-ideal power/ground effects. Specifically,

- Level 1 Trace and via couplings not considered, ideal P/G

- Level 2 Trace and via couplings considered, ideal P/G

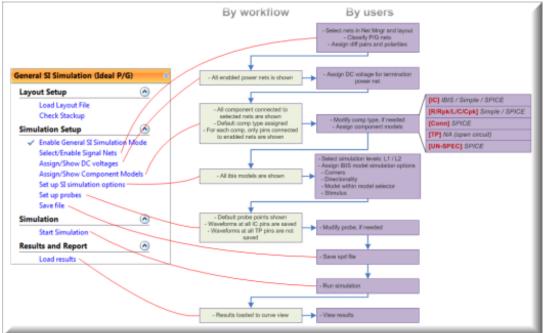

The main steps for simulation setup are shown in the following block diagram.

### **Tutorial Summary**

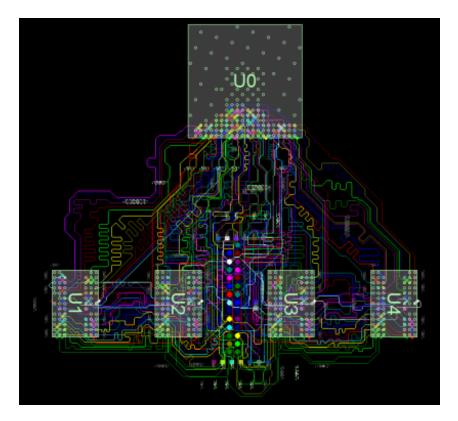

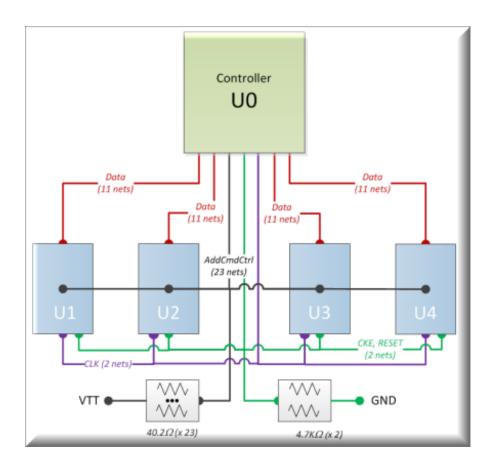

The sample case used in this tutorial contains one controller and four DRAMs as shown below.

1

In this tutorial, all DDR nets are included in analysis. The topology is as the following figure shows.

The following three original files are used in this tutorial:

- Tutorial\_GSI.spd layout file

- dram\_IO.ibs IBIS file containing DRAM buffer models

- ctrl\_IO.ibs IBIS file containing Ctrl buffer models

- They are all located in: <INSTALL\_DIR>\SpeedXP\Samples\SPEED2000\General SI Simulation\Examples\_PreSetup\

The completed sample and IBIS files (with step by step setup introduced in this tutorial) are also provided and located in:

<INSTALL\_DIR>\SpeedXP\Samples\SPEED2000\General SI Simulation \Examples\_PostSetup\Tutorial-1

#### General SI Simulation (Ideal P/G) workflow will lead user to:

- Setup simulation parameters

- Run simulation

- View simulation results

## Layout Setup

This chapter describes how to load layout file and check stackup.

1. Launch SPEED2000 Generator , and select the General SI Simulation (Ideal P/G) workflow.

2. Click **Load Layout File** to load tutorial\_GSI.spd. The workflow step **Check Stackup** is enabled.

Layout Setup Load Layout File Check Stackup

3. Click Check Stackup to open the Layer manager -> Stack Up window.

| Løyer #    | Color     | Layer Icon   | Layer Name        | Thickness( | Material | Conductivity(S | Pil-in Dielectric | Permittivity | Loss Tangent                      | Shape Name     | T  |

|------------|-----------|--------------|-------------------|------------|----------|----------------|-------------------|--------------|-----------------------------------|----------------|----|

|            |           |              | Signal\$_TOP      | 0.04064    |          | 5.959e+007     |                   | [1]          | [0]                               | Shape\$TOP     | 0. |

|            | _         |              | Medium\$41        | 0.07747    |          | 0              |                   | 3.9          | 0.035                             |                |    |

|            |           |              | Signal#L2_GND1    | 0.01524    |          | 5.959e+007     |                   | [4.09]       | [0.035]                           | Shape\$L2      | 0. |

|            |           |              | Medium\$43        | 0.0762     |          | 0              |                   | 4.28         | 0.035                             |                |    |

|            |           |              | Signal9.3_SIG1    | 0.01524    |          | 5.959e+007     |                   | [4.09]       | [0.035]                           | Shape\$L3_SIG1 | ٥. |

|            |           |              | Medium\$45        | 0.14351    |          | 0              |                   | 3.9          | 0.035                             |                |    |

|            |           |              | Signal\$.4_GND2   | 0.01524    |          | 5.959e+007     |                   | [4.09]       | [0.035]                           | Shape\$1.4     | 0, |

|            |           |              | Medium\$47        | 0.0762     |          | 0              |                   | 4.28         | 0.035                             |                |    |

|            |           |              | Signal\$1.5_SIG2  | 0.01524    |          | 5.959e+007     |                   | [4.09]       | [0.035]                           | Shape\$L5_SUG2 | 0. |

|            |           |              | Medium\$49        | 0.142494   |          | 0              |                   | 3.9          | 0.035                             |                |    |

|            |           |              | Signal#L6_GND3    | 0.03048    |          | 5.959e+007     |                   | [4.24]       | [0.035]                           | Shape\$L6      | 0. |

|            |           |              | Medum\$51         | 0.2032     |          | 0              |                   | 4.58         | 0.035                             |                |    |

|            |           |              | Signal\$.7_PWR1   | 0.03048    |          | 5.959e+007     |                   | [4.32]       | [0.035]                           | Shape\$L7_P    | ٥. |

|            |           |              | Medum\$53         | 0.2413     |          | 0              |                   | 4.06         | 0.035                             |                |    |

|            |           |              | Signal\$.8_PWR2   | 0.03048    |          | 5.959e+007     |                   | [4.32]       | [0.035]                           | Shape\$L8_P    | ٥. |

|            |           |              | Medium\$55        | 0.2032     |          | 0              |                   | 4.58         | 0.035                             |                |    |

|            |           |              | Signal\$.11_GND4  | 0.03048    |          | 5.959e+007     |                   | [4.24]       | [0.035]                           | Shape\$L11     | 0. |

|            |           |              | Medium\$61        | 0.142494   |          | 0              |                   | 3.9          | 0.035                             |                |    |

| )          |           |              | Signal\$.12_SIG3  | 0.01524    |          | 5.959e+007     |                   | [4.09]       | [0.035]                           | Shape\$L12     | 0. |

|            |           |              | Medium\$63        | 0.0762     |          | 0              |                   | 4.28         | 0.035                             |                |    |

|            |           |              | Signal\$.13_GND5  | 0.01524    |          | 5.959e+007     |                   | [4.09]       | [0.035]                           | Shape\$L13     | ٥. |

|            |           |              | Medium\$65        | 0.144272   |          | 0              |                   | 3.9          | 0.035                             |                |    |

|            |           |              | Signal 9, 14 SIG4 | 0.01524    |          | 5.959e+007     |                   | [4.09]       | 0.035]                            | Shape\$1.14    | 0, |

| otal Thick | ness: 2.0 | 0053e+000 mm |                   |            |          |                |                   | port Auto    | View Materia<br>Set Layer Special |                |    |

- 4. Check the stackup and edit as desired (no changes in this example).

- 5. Click **OK** to exit the window.

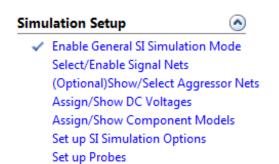

## **Simulation Setup**

This chapter introduces how to set up simulation parameters for general SI simulation.

Click Enable General SI Simulation Mode to enable General SI simulation mode.

Save File

When enabled, a check mark  $\checkmark$  appears ahead the workflow step. And all other related steps are enabled.

### **Enabling Simulation Nets**

To perform general SI simulation with SPEED2000, you'll need to select simulation nets first and define the differential pair property.

- Click Select/Enable Signal Nets in the Workflow pane. The Net Manager appears in the right side of the window.

- 2. Select to enable power net  $\ensuremath{\text{VTT}}$  .

July 2014

З

| Net Manager          | ×           |

|----------------------|-------------|

| Net:                 | - 🔎         |

| Show Coupled Line    | -           |

| Net List (Sort all)  | %Coupling 📥 |

| 🗌 📿 🌠 Unnamed Net(s) | 2           |

| 🖃 🗹 🎽 PowerNets      |             |

| 🗖 📿 💆 VDD            | 2           |

| VTT 🗹                | 2           |

| 🗖 📿 🖊 VTT_REF        | 2 ≡         |

| 😑 🔲 📿 🌌 GroundNets   |             |

| 🗖 📿 💆 GND            | 2           |

| 🗖 📿 🗖 A0             | 2           |

| 🗖 📿 📈 A1             | 2           |

| 🗖 📿 📈 A2             | 2           |

| 🗖 📿 🔀 A3             | 2           |

- 3. Choose all signal nets.

- 4. Right-click and choose **Enable Selected Nets** from the pop-up menu.

All selected nets are enabled.

The diff-pair and polarity are guessed out automatically.

- If the diff-pair is not guessed out, choose both positive and negative nets, right-click and choose Classify as diff pair to define it manually.

- If the polarity is not guessed out, right-click the positive net and choose Switch Polarity to define it manually.

### Assigning DC Voltage

If power or ground nets are enabled as simulation nets, the DC voltage should be assigned before simulation.

- 1. Click Assign/Show DC Voltages in the Workflow pane. The Assign/Show DC Voltages window opens.

- 2. Input **0.75V** for **VTT** net like the following figure shows.

| Net Name | Volt(V)         |  |

|----------|-----------------|--|

| Zm       | Volt(V)<br>0.75 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

|          |                 |  |

3. Click OK .

### **Assigning Component Models**

This section introduces how to assign models to all components.

### Assigning IBIS Model to IC Component U0

- 1. Click Assign/Show Component Models in the Workflow pane. The Set up Component Models window opens.

- 2. Select to highlight component **U0** and click the **Edit Model** button.

| Comp Name                 | Comp Type | Part Name                                                |            |

|---------------------------|-----------|----------------------------------------------------------|------------|

| U0                        | IC        | Controller                                               |            |

| 04                        | IC        | Dram                                                     |            |

| U1                        | IC        | Dram                                                     |            |

| U2                        | IC        | Dram                                                     |            |

| U3<br>R325                | IC        | Dram                                                     |            |

|                           | R         | R_0402_40_2<br>R_0402_40_2                               |            |

| R326<br>R327              | R         | R_0402_40_2                                              |            |

| R328                      | R         | R_0402_40_2                                              |            |

|                           | -         |                                                          |            |

|                           |           | 111                                                      |            |

| ssign models              |           |                                                          |            |

| Assign IBIS m             | odels     | Assign simple termination models     Assign SPICE models | O Value 0  |

|                           |           |                                                          |            |

| IBIS File:<br>Copy IBIS N | fodel to  | Edit Model                                               | Component: |

|                           | fodel to  | Edit Model                                               | Component: |

|                           | fodel to  | Edit Model                                               | Component: |

|                           | fodel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | fodel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

|                           | todel to  | Edit Model                                               | Component: |

The Assign IBIS models window opens.

3. Browse to load the IBIS file ctrl\_IO.ibs.

| Assign IBIS models                            |                                  |                |                                     |                                                                                                 | □ ×   |

|-----------------------------------------------|----------------------------------|----------------|-------------------------------------|-------------------------------------------------------------------------------------------------|-------|

| Layout Comp Name:                             | <u>uo</u>                        |                | IBIS Model File:<br>IBIS Component: | x=3\SpeedXP\Samples\SPEED2000\General SI Simulation\Example_PreSetup\ctrl_IO.ibs         DDR3_j |       |

| LayoutPinName /<br>NetName (Sort By ∠<br>Net) | IBISModelPinName /<br>SignalName | Model Name     |                                     |                                                                                                 |       |

| M4 / A0                                       |                                  |                |                                     |                                                                                                 |       |

| M5 / A1                                       |                                  |                |                                     |                                                                                                 |       |

| K4 / A2                                       |                                  |                |                                     |                                                                                                 |       |

| L4 / A3                                       |                                  |                |                                     |                                                                                                 |       |

| K6 / A4                                       |                                  |                |                                     |                                                                                                 |       |

| K5 / A5                                       |                                  |                |                                     |                                                                                                 |       |

| J7 / A6                                       |                                  |                |                                     |                                                                                                 |       |

| J6 / A7<br>J5 / A8                            |                                  |                |                                     |                                                                                                 |       |

| H5 / A9                                       |                                  |                |                                     |                                                                                                 |       |

| J3 / A10                                      |                                  |                |                                     |                                                                                                 |       |

| G5 / A11                                      |                                  |                |                                     |                                                                                                 |       |

| H4 / A12                                      |                                  |                |                                     |                                                                                                 | -     |

| Package Model :                               | lone O Pin RLC O                 | Package Model: |                                     | Clear All Recover OK Ca                                                                         | ancel |

The IBIS file is loaded.

- 4. Use Shift and Ctrl keys to select multiple nets A0 CKE,  $CS_B$ , ODT,  $RAS_B$ ,  $RESET_B$ , and  $WE_B$ .

- 5. Click the icon is in the field of **Model Name** column and select **cmd\_ctrl** from the pop-up window.

| LayoutPinName /<br>NetName (Sort By /<br>Net) | 1815ModelPinName /<br>SignalName | Model Name    |             |                                                             |

|-----------------------------------------------|----------------------------------|---------------|-------------|-------------------------------------------------------------|

| M4 / A0                                       |                                  |               |             |                                                             |

| M5 / A1                                       |                                  |               |             |                                                             |

| K4 / A2                                       |                                  |               |             |                                                             |

| L4 / A3                                       |                                  |               |             |                                                             |

| L4 / A3<br>K6 / A4                            |                                  |               |             |                                                             |

| KS / AS                                       |                                  |               |             |                                                             |

| 17 / A6                                       |                                  |               |             |                                                             |

| 36 / A7                                       |                                  |               |             |                                                             |

| 35 / A8                                       |                                  |               |             |                                                             |

| H5 / A9                                       |                                  |               |             |                                                             |

| J3 / A10                                      |                                  |               |             |                                                             |

| 65 / A11                                      |                                  | Pin Name      | Signal Name | Model Name                                                  |

| H1 / A12                                      |                                  | Not Connected |             |                                                             |

| F4 / A13                                      |                                  | not corrected |             | data                                                        |

| G4 / A14                                      |                                  |               |             | dk                                                          |

| L7 / BAO                                      |                                  |               |             | and ctri                                                    |

| LG / BA1                                      |                                  |               |             | data_odt100                                                 |

| HG / BA2                                      |                                  |               |             | data_odtoff                                                 |

| P3 / CAS_8                                    |                                  |               |             | GND                                                         |

| V3 / CKE                                      |                                  |               |             | POWER                                                       |

| N5 / CLK_N                                    |                                  |               |             | Ponds                                                       |

| N4/CLK_P                                      |                                  |               |             |                                                             |

| P6 / CS_8                                     |                                  |               |             |                                                             |

| 81 / DM0                                      |                                  |               |             |                                                             |

| 13 / DM1                                      |                                  |               |             |                                                             |

| P1/DM2                                        |                                  |               |             |                                                             |

| AA2 / DM3                                     |                                  |               |             |                                                             |

| E3 / DQ0                                      |                                  | OK            | Cancel      | Model Selector name is italic and underlined.               |

| C3/DQ1                                        |                                  |               | Carice      | The second second second with a second with a second second |

#### 6. Click **OK** .

The selected nets are assigned with the model **cmd\_ctrl** .

| LayoutPinName /<br>NetName (Sort By<br>Net) | IBISModelPinName /<br>SignalName | Model Name |

|---------------------------------------------|----------------------------------|------------|

| M4 / A0                                     | M4 / A0                          | cmd_ctrl   |

| M5 / A1                                     | M5/A1                            | and_ctrl   |

| K4 / A2                                     | K4/A2                            | and_ctrl   |

| L4 / A3                                     | L4/A3                            | cmd_ctrl   |

| K6 / A4                                     | K6 / A4                          | cmd_ctrl   |

| K5 / A5                                     | K5 / A5                          | and_ctrl   |

| 37 / A6                                     | J7 / A6                          | cmd_ctrl   |

| J6 / A7                                     | J6 / A7                          | cmd_ctrl   |

| J5 / A8                                     | J5 / A8                          | and_ctrl   |

| H5 / A9                                     | H5 / A9                          | cmd_ctrl   |

| J3 / A10                                    | J3 / A10                         | cmd_ctrl   |

| G5 / A11                                    | G5 / A11                         | and_ctrl   |

| H4 / A12                                    | H4/A12                           | and_ctrl   |

| F4 / A13                                    | F4/A13                           | cmd_ctrl   |

| G4 / A14                                    | G4/A14                           | and_ctrl   |

| L7 / BA0                                    | L7/8A0                           | cmd_ctrl   |

| L6 / BA1                                    | L6 / BA1                         | and_ctrl   |

| M6 / BA2                                    | M6 / BA2                         | and_ctrl   |

| P3 / CAS_B                                  | P3/CAS_B                         | cmd_ctrl   |

| V3 / CKE                                    | V3/OKE                           | and_ctrl   |

| N5/CLK_N                                    |                                  |            |

| N4/CLK_P                                    |                                  |            |

| P6 / CS_8                                   | P6 / CS_8                        | and_ctrl   |

| B1 / DM0                                    |                                  |            |

7. Repeat the above steps to assign nets CLK\_N and CLK\_P with the model clk .

| L7 / BA0   | L7 / BAO | cmd_ctrl |  |

|------------|----------|----------|--|

| L6 / BA1   | L6 / BA1 | cmd_ctrl |  |

| M6 / BA2   | M6 / BA2 | cmd_ctrl |  |

| P3 / CAS_B | P3/CAS_B | cmd_ctrl |  |

| V3 / CKE   | V3/CKE   | cmd_ctrl |  |

| NS / CLK_N | NS/CLK_N | dk       |  |

| N4/CLK_P   | N4/CLK_P | dk       |  |

| P6 / CS_B  | P6/CS_B  | cmd_ctrl |  |

| B1 / DM0   |          |          |  |

8. Repeat the above steps to assign nets  $DMO - DQS3_P$  with the model data . All nets are assigned with IBIS models.

| 1                          | 3                  |            |

|----------------------------|--------------------|------------|

| LayoutPinName /            | IBISModelPinName / | Model Name |

| NetName (Sort By /<br>Net) | SignalName         |            |

|                            |                    |            |

| M4 / A0                    | M4 / AD            | cmd_ctrl   |

| M5 / A1                    | M5/A1              | cmd_ctrl   |

| K4 / A2                    | K4/A2              | cmd_ctrl   |

| L4 / A3                    | L4/A3              | cmd_ctrl   |

| K6 / A4                    | K6 / A4            | and_ctrl   |

| KS / AS                    | K5 / A5            | cmd_ctrl   |

| 37 / A6                    | 17 / A6            | cmd_ctrl   |

| 36 / A7                    | J6 / A7            | cmd_ctrl   |

| 35 / A8                    | 35 / A8            | cmd_ctrl   |

| H5 / A9                    | H5 / A9            | cmd_ctrl   |

| J3 / A10                   | J3 / A10           | and_ctrl   |

| G5 / A11                   | G5/A11             | cmd_ctrl   |

| H4 / A12                   | H4/A12             | and_ctrl   |

| F4/A13                     | F4/A13             | and atri   |

| G4 / A14                   | G4/A14             | end etri   |

| L7 / BA0                   | L7 / BA0           | and atri   |

| LG / BA1                   | L6/BA1             | and atri   |

| M6 / BA2                   | M6 / BA2           | end etri   |

| P3 / CAS_B                 | P3/CAS_B           | and atri   |

| V3 / CKE                   | V3/OE              | and atri   |

| N5/CLK N                   | N5 / CLK_N         | dk         |

| N4/CLK P                   | N4/CLK_P           | dk         |

| P6 / CS_8                  | P6/C5_8            | cmd_ctrl   |

| B1 / DM0                   | 81/DM0             | data       |

| H3 / DM1                   | H3/DM1             | data       |

| P1/DM2                     | P1/DM2             | data       |

| AA2 / DM3                  | AA2 / DM3          | data       |

| E3 / DQ0                   | E3/DQ0             | data       |

| C3 / DQ1                   | C3/DQ1             | data       |

| F2 / DQ2                   | F2/DQ2             | data       |

| D1/DQ3                     | D1/DQ3             | data       |

| F1/004                     | F1/DQ4             | data       |

| 111004                     | 11004              | 0000       |

| E1/DQ5       | E1/DQ5       | data     |

|--------------|--------------|----------|

| 82 / DQ6     | 82/DQ6       | data     |

| D3 / DQ7     | D3 / DQ7     | cheta    |

| G2 / DQ8     | G2/DQ8       | data     |

| L1 / DQ9     | L1/DQ9       | data     |

| G1 / DQ10    | G1/DQ10      | clata    |

| K1/DQ11      | K1/DQ11      | data     |

| L3 / DQ12    | L3/DQ12      | data     |

| L2 / DQ13    | L2/DQ13      | data     |

| J1 / DQ14    | J1/DQ14      | data     |

| K3 / DQ15    | K3/DQ15      | data     |

| M1 / DQ16    | M1/DQ16      | data     |

| T3 / DQ17    | T3/DQ17      | data     |

| N3 / DQ18    | N3 / DQ18    | dete     |

| T1 / DQ19    | T1/DQ19      | data     |

| R3 / DQ20    | R3 / DQ20    | data     |

| T2 / DQ21    | T2/DQ21      | data     |

| M2 / DQ22    | M2 / DQ22    | data     |

|              |              |          |

| R1/DQ23      | R1/DQ23      | data     |

| U1 / DQ24    | U1/DQ24      | data     |

| AA1 / DQ25   | AA1/DQ25     | data     |

| U2 / DQ26    | U2 / DQ26    | data     |

| AA3 / DQ27   | AA3 / DQ27   | cheta    |

| W1 / DQ28    | W1/DQ28      | data     |

| Y3 / DQ29    | Y3 / DQ29    | data     |

| W3 / DQ30    | W3 / DQ30    | data     |

| Y1 / DQ31    | Y1/DQ31      | data     |

| D2 / DQS0_N  | D2 / DQ50_N  | data     |

| C2 / DQS0_P  | C2/DQ50_P    | data     |

| J2 / DQS1_N  | J2 / DQ51_N  | data     |

| H2/DQS1 P    | H2/DOS1 P    | data     |

|              |              |          |

| P2 / DQS2_N  | P2 / DQ52_N  | data     |

| N2 / DQS2_P  | N2/DQS2_P    | data     |

| W2 / DQS3_N  | W2/DQ53_N    | data     |

| V2 / DQS3_P  | V2/DQ53_P    | data     |

| P5 / ODT     | P5/ODT       | cmd_ctrl |

| R5 / RAS_B   | R5/RAS_B     | cmd_ctrl |

| F3 / RESET_B | F3 / RESET_B | and atri |

| R4/WEB       | R4/WEB       | and atri |

|              |              | 0.00_001 |

9. Check the newly generated models and click OK .

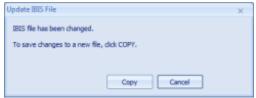

The Update IBIS File dialog box opens to confirm the changes.

10. Click Copy.

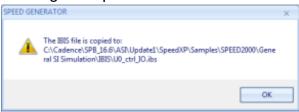

A dialog box opens.

11. Click  $\mathbf{OK}$  to create a new IBIS model.

The **Assign IBIS models** window quits and a pin matched component IBIS model for controller **U0** is generated, located in the sub-folder named **IBIS** under the project folder.

| SpeedXP + Samples + SPEED2000 + Genera | al SI Simulation 🕨 IBIS | •        |

|----------------------------------------|-------------------------|----------|

| brary 🕶 Share with 👻 Burn New fo       | older                   |          |

| Name                                   | Date modified           | Туре     |

| U0_ctrl_I0.ibs                         | 12/3/2013 1:56 PM       | IBS File |

A green check mark appears ahead **U0** in the **Set up Component Models** window.

| Set u | p Component                             | Models                     |                                    | - × 0                           |  |

|-------|-----------------------------------------|----------------------------|------------------------------------|---------------------------------|--|

|       | Comp Name                               | Comp Type                  | Part Name                          | A                               |  |

| -     | UO                                      | 10                         | Controller                         | =                               |  |

|       | U4                                      | 1C                         | Dram                               |                                 |  |

|       | U1                                      | 1C                         | Dram                               |                                 |  |

|       | U2                                      | 1C                         | Dram                               |                                 |  |

|       | U3                                      | 1C                         | Dram                               |                                 |  |

|       | R325                                    | R                          | R_0402_40_2                        |                                 |  |

|       | R326                                    | R                          | R_0402_40_2                        |                                 |  |

|       | R327                                    | R                          | R_0402_40_2                        |                                 |  |

|       | R328                                    | R                          | R_0402_40_2                        | *                               |  |

| 1     |                                         |                            |                                    | •                               |  |

|       | ssign models<br>Assign 1815 m           | odels                      | O Assign simple termination models | O Assign SPICE models O Value 0 |  |

|       | IIS models<br>IBIS File:<br>Copy IBIS N | 1815'(J.O_ct+1<br>4odel to | JO.bs Edit Model                   | Component: DDR3_j               |  |

#### Assigning IBIS Model to IC Component U1

- 1. Select to highlight component **U1** and click the **Edit Model** button. The **Assign IBIS models** window opens.

- 2. Browse to load the IBIS file dram\_IO.ibs.

| Layout Comp Name:                             | UI                               |            | To use the IBIS model from AMM libraries, please click AMM Library IBIS Model File: 115peed/07/Samples/SPEED2000/(DR-650 Simulation/Examples_PreSetup)(ham_J0.bd) |

|-----------------------------------------------|----------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                               |                                  |            |                                                                                                                                                                   |

|                                               |                                  |            | 3815 Component: dram 16x4                                                                                                                                         |

|                                               |                                  |            |                                                                                                                                                                   |

| Layou/PinName /<br>NetName (Sort By /<br>Net) | IBISModelPinName /<br>SignalName | Model Name |                                                                                                                                                                   |

| K3 / A0                                       |                                  |            |                                                                                                                                                                   |

| 7 / A1                                        |                                  |            |                                                                                                                                                                   |

| 3/A2                                          |                                  |            |                                                                                                                                                                   |

| C2 / A3                                       |                                  |            |                                                                                                                                                                   |

| 8/ 44                                         |                                  |            |                                                                                                                                                                   |

| 12 / A5<br>MB / A6                            |                                  |            |                                                                                                                                                                   |

| M2 / A7                                       |                                  |            |                                                                                                                                                                   |

| NS / AS                                       |                                  |            |                                                                                                                                                                   |

| MG / A9                                       |                                  |            |                                                                                                                                                                   |

| H7 / A10                                      |                                  |            |                                                                                                                                                                   |

| M7 / A11                                      |                                  |            |                                                                                                                                                                   |

|                                               |                                  |            |                                                                                                                                                                   |

The IBIS file is loaded.

- 3. Repeat the steps described in the above section to assign nets A0 CKE,  $CS_B$ , ODT,  $RAS_B$ ,  $RESET_B$ , and  $WE_B$  with the model INPUT.

- 4. Assign nets CLK\_N and CLK\_P with the model CLKIN .

- 5. Assign nets  $DMO DQ_7$  with the model DQ.

- 6. Assign nets **DQS0\_N** and **DQS0\_P** with the model **DQS** . All nets are assigned with the IBIS models.

| LayoutPinName /<br>NetName (Sort By /<br>Net) | IBISModelPinName /<br>SignalName | Model Name   |

|-----------------------------------------------|----------------------------------|--------------|

| K3 / A0                                       | K3 / A0                          | INPLIT       |

| L7 / A1                                       | L7/A1                            | INPUT        |

| L3 / A2                                       | L3/A2                            | INPLIT       |

| K2 / A3                                       | K2 / A3                          | INPUT        |

| L8 / A4                                       | L8 / A4                          | INPLIT       |

| L2 / A5                                       | L2/A5                            | INPUT        |

| MB / A6                                       | M8 / A6                          | INPUT        |

| M2 / A7                                       | M2 / A7                          | INPUT        |

| NB / AB                                       | N8 / A8                          | INPUT        |

| M3 / A9                                       | M3 / A9                          | INPUT        |

| H7 / A10                                      | H7/A10                           | INPUT        |

| M7 / A11                                      | M7/A11                           | INPLIT       |

| K7 / A12                                      | K7 / A12                         | INPUT        |

| N3 / A13                                      | N3/A13                           | INPLIT       |

| N7 / A14                                      | N7/A14                           | INPUT        |

| 32 / BAO                                      | 32/BAD                           | INPLIT       |

| KB / BA1                                      | K8 / 8A1                         | INPUT        |

| 33 / BA2                                      | 33/BA2                           | INPUT        |

| G3 / CAS_B                                    | G3/CAS_B                         | IMPUT        |

| G9 / CKE                                      | G9 / CKE                         | INPUT        |

| G7 / CLK_N                                    | G7/CLK_N                         | CLKIN        |

| F7/CUK_P                                      | F7/CLK_P                         | <u>a.kin</u> |

| H2 / CS_B                                     | H2/CS_B                          | INPLIT       |

| 87 / DM0                                      | 87 / DM0                         | 00           |

| B3 / DQ0                                      | B3 / DQ0                         | 00           |

| C7 / DQ1                                      | C7/DQ1                           | 00           |

| C2 / DQ2                                      | C2/DQ2                           | 00           |

| C8 / DQ3                                      | C8 / DQ3                         | 00           |

| E3 / DQ4                                      | E3 / DQ4                         | 00           |

| EB / DQ5                                      | E8 / DQ5                         | DQ           |

| D2 / DQ6                                      | D2/DQ6                           | 00           |

| F7 ( 007                                      | 57 (007                          | 00           |

| E7 / DQ7                                      | E7 / DQ7                         | 00           |

| D3 / DQS0_N                                   | D3/DQ50_N                        | 005          |

| C3 / DQS0_P                                   | C3/DQ60_P                        | DQS          |

| G1 / ODT                                      | G1/ODT                           | INPUT        |

| F3 / RAS_B                                    | F3/RAS_B                         | INPUT        |

| N2 / RESET_B                                  | N2/RESET_B                       | INPUT        |

| H3 / WE_B                                     | H3/WE_B                          | INPUT        |

7. Check the newly generated models and click OK .

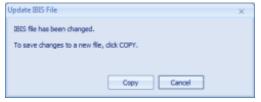

The **Update IBIS File** dialog box opens to confirm changes.

8. Click Copy.

A dialog box opens.

9. Click  $\mathbf{OK}$  to create a new IBIS model.

The **Assign IBIS models** window quits and a pin matched component IBIS model for controller **U1** is generated, located in the sub-folder named **IBIS** under the project folder.

| SpeedXP + Samples + SPEED2000 + | General SI Simulation + IBIS           | <b>▼ 4</b> 9 St      |

|---------------------------------|----------------------------------------|----------------------|

| rary 🔻 Share with 🖛 Burn        | New folder                             |                      |

| Name                            | Date modified                          | Туре                 |

| U0_ctrl_J0.ibs                  | 12/3/2013 1:56 PM<br>12/3/2013 2:16 PM | IBS File<br>IBS File |

A green check mark appears ahead **U1** in the **Set up Component Models** window.

|     | Comp Name                     | Comp Type   | Part Name                                   | <u> </u>                   |

|-----|-------------------------------|-------------|---------------------------------------------|----------------------------|

| ~   | UO                            | IC          | Controller                                  |                            |

|     | U4                            | 1C          | Dram                                        |                            |

| ~   | U1                            | IC .        | Dram                                        |                            |

|     | U2                            | IC          | Dram                                        |                            |

|     | U3                            | IC          | Dram                                        |                            |

|     | R325                          | R           | R_0402_40_2                                 |                            |

|     | R326                          | R           | R_0402_40_2                                 |                            |

|     | R327                          | R           | R_0402_40_2                                 |                            |

|     | R328                          | R           | R_0402_40_2                                 |                            |

| 11  |                               |             |                                             | •                          |

| (   | sign models<br>Assign 1815 mo | dels        | O Assign simple termination models O Assign | SPICE models Value 0 Value |

| -18 | IS models                     |             |                                             |                            |

|     | IBIS File:                    | 1B1S\U1_dra | 1JO.bs Edit Model                           | Component: dram16x4        |

|     | Copy IBIS M                   | odel to     |                                             |                            |

### Copying IBIS Model to U2, U3 and U4 from U1

- 1. Click the **Copy IBIS Model to** button. The **IBIS Copy** window opens.

- 2. Select to check the components U4 , U2 and U3 (uncheck U0 ).

| Comp No | 100 |  |  |   |

|---------|-----|--|--|---|

|         | UD  |  |  | - |

|         | U4  |  |  |   |

|         | U2  |  |  |   |

|         | U3  |  |  |   |

|         |     |  |  |   |

| _       |     |  |  |   |

| -       |     |  |  |   |

|         |     |  |  |   |

|         |     |  |  |   |

|         |     |  |  |   |

|         |     |  |  |   |

|         |     |  |  |   |

| _       |     |  |  |   |

3. Click **OK** .

All nets for component **U2**, **U3** and **U4** are assigned with IBIS models. A green check mark appears ahead components **U4**, **U2** and **U3** in the **Set up Component Models** window.

|   | Comp Name      | Comp Type    | Part Name                        |                     |                                       | * |

|---|----------------|--------------|----------------------------------|---------------------|---------------------------------------|---|

| ~ | 00             | IC           | Controller                       |                     |                                       |   |

| ~ | U4             | IC           | Dram                             |                     |                                       |   |

| ~ | U1             | IC           | Dram                             |                     |                                       |   |

|   | U2             | IC           | Dram                             |                     |                                       |   |

|   | U3             | IC           | Dram                             |                     |                                       |   |

| ~ | R325           | R            | R_0402_40_2                      |                     |                                       |   |

| ~ | R326           | R            | R_0402_40_2                      |                     |                                       |   |

| ~ | R327           | R            | R_0402_40_2                      |                     |                                       |   |

|   | R328           | R            | R_0402_40_2                      |                     |                                       | + |

| 1 |                |              |                                  | 1                   | • • • • • • • • • • • • • • • • • • • |   |

| - | ssign models   |              |                                  |                     |                                       |   |

| 0 | Assign IBIS mo | dels         | Assign simple termination models | Assign SPICE models | O Value □                             |   |

| _ | NS models      |              |                                  |                     |                                       |   |

| - | us modes       |              |                                  |                     |                                       |   |

|   | IBIS File:     | IBIS\U1_drar | _10.bs Edit Model                |                     | Component: dram16x4                   |   |

| ſ | Copy IBIS M    | odel to      |                                  |                     |                                       |   |

#### **Defining Passive Component Value**

The value of passive component is generated automatically by default. It is changeable. You can check and modify it as desired.

- 1. Select components R319 and R320 .

- 2. Input 4700ohm in the field of Value .

| Comp Name     | Comp Type    | Part Name   |

|---------------|--------------|-------------|

| R342          | R            | R_0402_40_2 |

| R343          | R            | R 0402 40_2 |

| R344          | R            | R_0402_40_2 |

| R345          | R            | R_0402_40_2 |

| R346          | R            | R_0402_40_2 |

| R347          | R            | R_0402_40_2 |

| R319          | R            | R_0402_4_7K |

| R320          | R            | R_0402_4_7K |

| R323          | R            | R_0402_80_6 |

|               |              |             |

| e: Comp Type  | is editable. |             |

| ssign models- |              |             |

3. Click **OK** .

The Set up Component Models window quits.

### **SI Simulation Options Setup**

This section introduces how to set up SI simulation options.

Click Set up SI Simulation Options in the Workflow pane.

The GeneralSI simulation setup -> GeneralSI Options pane appears at the bottom of the window.

| ralSI Options Setup Probes          |        |      |                       |                 |                      |                   |                  |                  |      |

|-------------------------------------|--------|------|-----------------------|-----------------|----------------------|-------------------|------------------|------------------|------|

| mulation Configuration              |        | Hod  | els and Data patterns |                 |                      |                   |                  |                  |      |

| PJG and coupling options            | Corner | Deta | Rate: 1               | Sps Clack Perio | 6 T = 2 mi           | # of Bris: 10     | Tmax: 2.67819    | •                |      |

|                                     | Этур   | Cor  | Pr/Name/NetFiame      | 1/O Selection   | Transmitter 30 Model | Receiver IO Model | Stimulus Pattern | Stmuke Offset(s) | ut   |

| Evel-1: Ideal P/G, single line      |        | 8    | (IC) U0               |                 |                      |                   |                  |                  |      |

|                                     | OFest  |      | AA1/DQ25              | Un-assigned     | data_odtoff          | data_odtoff       | 3010303010       | 0                | \$T  |

| C Level-2: Ideal P/G, coupled lines | 0.001  |      | AA2/DH3               | Un-assigned     | dets_odtoff          | data_odtoff       | 3010303010       | 0                | IT   |

|                                     |        |      | AA3/DQ27              | Un-assigned     | data_odtoff          | data_odteff       | 3018303010       | 0                | 17   |

|                                     | Oslow  |      | 81/DM0                | Un-assigned     | data_odtoff          | data_odtoff       | 3010101010       | 0                | 3T   |

| Ideal P/G option simulation         |        |      | 82/DQ6                | Un-assigned     | data_odtoff          | data_odteff       | 3010303010       | 0                | 1T   |

|                                     |        |      | C2(DQS8_P             | Un-assigned     | data_odtoff          | data_odtoff       | 3018303010       | 0                | aT . |

| time step(ps): 20                   |        | -    | DQ/DQS0_N             | Un-assigned     | data_pdtoff          | data_odtoff       | 0101010101       | 0                | IT   |

| Counting (NA) 5                     |        |      | D1/DQ3                | Un-assigned     | data_odtoff          | data_odteff       | 3018303010       | 0                | 17   |

| Coupling (%): 5                     |        |      | C3/DQ1                | Un-assigned     | data_pdtoff          | data_odtoff       | 3010101010       | 0                | ST.  |

| Rice Time(pc): 300                  |        |      | 03/DQ7                | Un-assigned     | data_odtoff          | data_odtoff       | 3010303010       | 0                | TT.  |

| Land Landborn Land                  |        |      | ENDOS                 | its-acciment    | data officity        | data odioff       | 1010101010       | 0                | ST   |

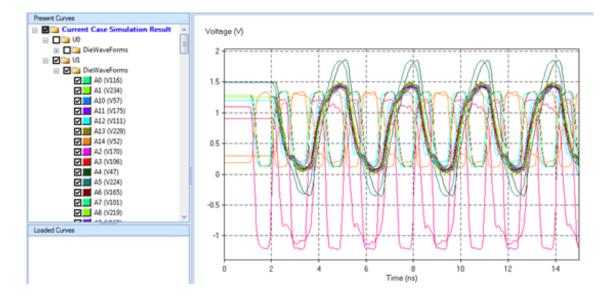

The pane contains two tabs: GeneralSI Options and Setup Probes .

#### **General SI Options**

- 1. Input the following models and data parameters:

- Data Rate : 1.333Gbps

- # of Bits : 10

- Tmax : 15ns

| _ | - Models and D | ata natterne |      |                   |             |            |    |       |    |      |   |  |

|---|----------------|--------------|------|-------------------|-------------|------------|----|-------|----|------|---|--|

|   | Prodeb drid b  | ous pouch is | ,    |                   |             |            |    |       |    |      |   |  |

|   |                |              |      |                   |             |            |    |       |    | <br> | _ |  |

|   | Data Rate:     | 1.333        | Gbps | Clock Period: T = | 1.500375 NS | # of Bits: | 10 | Tmax: | 15 | ns   |   |  |

|   |                |              |      |                   |             |            |    |       |    |      | - |  |

#### 2. Click the column title **CompPinName/Netname** to reorder the nets alphabetically.

| CompPinName/NetName(Sor<br>NetName) |         | I/O Selection | Transmitter IO Model | Receiver IO Model | Stimulus Pattern | Stimulus Offset(s) | UI |

|-------------------------------------|---------|---------------|----------------------|-------------------|------------------|--------------------|----|

|                                     | [IC] U0 |               |                      |                   |                  |                    |    |

|                                     | M4/A0   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | M5/A1   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | K4/A2   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | L4/A3   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | K6/A4   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | K5/A5   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | J7/A6   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | J6/A7   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | J5/A8   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | H5/A9   | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | J3/A10  | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | G5/A11  | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | H4/A12  | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | F4/A13  | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | G4/A14  | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | L7/BA0  | Un-assigned   | cmd_ctrl             | cmd_ctrl          | 1010101010       | 0                  | 1T |

|                                     | 16/BA1  | Hn-assigned   | and and              | and and           | 1010101010       | 0                  | 17 |

#### **U0** Parameters Setup

- 1. Select to highlight the nets  $A0 WE_B$  under U0.

- 2. Click the icon is in the field of **I/O Selection** column and select **Output** from the drop-down list.

| Compl<br>NetNa |            | I/O Selection | Transmitter 10 Model            | Receiver IO Model | Stimulus Pattern | Stimulus Offset(s) | τιτ |

|----------------|------------|---------------|---------------------------------|-------------------|------------------|--------------------|-----|

|                | W3/DQ30    | Output        | <ul> <li>data_odtoff</li> </ul> |                   | 10 10 10 10 10   | 0                  | 117 |

|                | Y1/DQ31    | Un-assigned   | data_odtoff                     |                   | 1010101010       | 0                  | រា  |

| ⊕              | C2/DQS0_P  | Input         | data_odtoff                     |                   | 1010101010       | 0                  |     |

|                | D2/DQS0_N  | Output        | data_odtoff                     |                   | 0101010101       | 0                  | 117 |

| Ð              | H2/DQS1_P  | Output        | data_odtoff                     |                   | 1010101010       | 0                  | 11  |

| L              | J2/DQS1_N  | Output        | data_odtoff                     |                   | 0101010101       | 0                  | 1T  |

| ⊕              | N2/DQS2_P  | Output        | data_odtoff                     |                   | 1010101010       | 0                  |     |

|                | P2/DQ52_N  | Output        | data_odtoff                     |                   | 0101010101       | 0                  | 117 |

| Ð              | V2/DQ53_P  | Output        | data_odtoff                     |                   | 1010101010       | 0                  | 1T  |

| L              | W2/DQS3_N  | Output        | data_odtoff                     |                   | 0101010101       | 0                  | 117 |

|                | PS/ODT     | Output        | and_ctrl                        |                   | 10 10 10 10 10   | 0                  | 117 |

|                | R5/RAS_B   | Output        | and_ctrl                        |                   | 10 10 10 10 10   | 0                  | 117 |

|                | F3/RESET_B | Output        | and_ctrl                        |                   | 1010101010       | 0                  | 1T  |

|                | R4/WE_B    | Output        | cmd_ctrl                        |                   | 1010101010       | 0                  | 17  |

- 3. Select to highlight nets  $DMO DQS3_N$ .

- 4. Click the icon 토 in the field of **UI** column and input **0.5T** in the field.

| Compl<br>NetNa | PinName/NetName(Sor | I/O Selection | Transmitter 10 Model | Receiver IO Model | Stimulus Pattern | Stimulus Offset(s) | ur   |

|----------------|---------------------|---------------|----------------------|-------------------|------------------|--------------------|------|

|                | R 1/DQ23            | Output        | data_odtoff          |                   | 10 10 10 10 10   | 0                  | 1T   |

|                | U1/DQ24             | Output        | data_odtoff          |                   | 1010101010       | 0                  | 1T   |

|                | AA1/DQ25            | Output        | data_odtoff          |                   | 10 10 10 10 10   | 0                  | 1T   |

|                | U2/DQ26             | Output        | data_odtoff          |                   | 1010101010       | 0                  | IT   |

|                | AA3/DQ27            | Output        | data_odtoff          |                   | 1010101010       | 0                  | 1T   |

|                | W1/DQ28             | Output        | data_odtoff          |                   | 1010101010       | 0                  | 11   |

|                | Y3/DQ29             | Output        | data_odtoff          |                   | 1010101010       | 0                  | 11   |

|                | W3/DQ30             | Output        | data_odtoff          |                   | 1010101010       | 0                  | 11   |

|                | Y1/DQ31             | Output        | data_odtoff          |                   | 1010101010       | 0                  | 11   |

| ⊕              | C2/DQS0_P           | Output        | data_odtoff          |                   | 1010101010       | 0                  | 0.5T |

| L              | D2/DQS0_N           | Output        | data_odtoff          |                   | 0101010101       | 0                  | 1T   |

| Ð              | H2/DQS1_P           | Output        | data_odtoff          |                   | 1010101010       | 0                  | 1T   |

| L              | 32/DQS1_N           | Output        | data_odtoff          |                   | 0101010101       | 0                  | 11   |

| Ð              | N2/DQS2_P           | Output        | data_odtoff          |                   | 10 10 10 10 10   | 0                  | 1T   |

| L              | P2/DQS2_N           | Output        | data_odtoff          |                   | 0101010101       | 0                  | iT   |

| <b>B</b>       | V2/DQ53_P           | Output        | data_odtoff          |                   | 10 10 10 10 10   | 0                  | 1T   |

| L              | W2/DQ53_N           | Output        | data_odtoff          |                   | 0101010101       | 0                  | 1T   |

|                | DEPORT              | Output        | and and              |                   | 1010101010       | 0                  | 17   |

#### **U1** Parameters Setup

- 1. Select to highlight nets DM0 DQS0\_N under U1.

- 2. Click the icon 토 in the field of **I/O Selection** column and select **Input** from the drop-down list.

| Compl<br>NetNa | PinName/NetName(Sor | I/O Selection | Transmitter IO Model | Receiver IO Model | Stimulus Pattern  | Stimulus Offset(s) | -ut |

|----------------|---------------------|---------------|----------------------|-------------------|-------------------|--------------------|-----|

| ⊕              | F7/CLK_P            | Input         |                      | CLKIN_1333        |                   |                    |     |

| _              | G7/CLK_N            | Input         |                      | CLKIN_1333        |                   |                    |     |

|                | H2/CS_B             | Input         |                      | INPUT_1333        |                   |                    |     |

|                | 87/DM0              | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  | 1T  |

|                | 83/DQ0              | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 10 10 10 10 10 10 | 0                  | 1T  |

|                | C7/DQ1              | Input         | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  |     |

|                | C2/DQ2              | Output        | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  | 1T  |

|                | C8/DQ3              | Un-assigned   | DQ5_34_1333          | DQ5_34_1333       | 1010101010        | 0                  | 11  |

|                | E3/DQ4              | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  | 1T  |

|                | E8/DQ5              | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  | 117 |

|                | D2/DQ6              | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  | 117 |

|                | E7/DQ7              | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  | 117 |

| ⊕              | C3/DQ50_P           | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 1010101010        | 0                  | 117 |

| -              | D3/DQ50_N           | Un-assigned   | DQ5_34_1333          | DQS_34_1333       | 0101010101        | 0                  | 117 |

|                | G1/ODT              | Input         |                      | INPUT_1333        |                   |                    |     |

|                | F3/RAS_B            | Input         |                      | INPUT_1333        |                   |                    |     |

|                | N2/RESET_B          | Input         |                      | INPUT_1333        |                   |                    |     |

|                | HOARE B             | Innut         |                      | TND (T 1333       |                   |                    |     |

- 3. Assign the nets **DM0 DQ7** with the **Receiver IO Model DQ\_34\_ODT60\_1333** from the drop-down list.

- 4. Assign the nets DQS0\_P DQS0\_N with Receiver IO Model DQS\_34\_ODT60\_1333 from the drop-down list.

|   | pPinName/NetName(Sor<br>Name) | 1/O Selection | Transmitter IO Model | Receiver IO Model | Stimulus Pattern | Stimulus Offset(s) | ut |

|---|-------------------------------|---------------|----------------------|-------------------|------------------|--------------------|----|

|   | 87/DM0                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | B3/DQ0                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | C7/DQ1                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | C2/DQ2                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | C8/DQ3                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | E3/DQ4                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | E8/DQ5                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | D2/DQ6                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

|   | E7/DQ7                        | Input         |                      | DQS_34_ODT60      |                  |                    |    |

| ⊕ | C3/DQS0_P                     | Input         |                      | DQS_34_00T60      |                  |                    |    |

| L | D3/DQS0_N                     | Input         |                      | DQS_34_00T60      |                  |                    |    |

|   | G1/ODT                        | Input         |                      | INPUT_1333        |                  |                    |    |

|   | F3/RAS_B                      | Input         |                      | INPUT_1333        |                  |                    |    |

|   | N2/RESET_B                    | Input         |                      | INPUT_1333        |                  |                    |    |

|   | H3/WE_B                       | Input         |                      | INPUT_1333        |                  |                    |    |

| 8 | [IC] U2                       |               |                      |                   |                  |                    |    |

|   | K3/A0                         | Input         |                      | INPUT_1333        |                  |                    |    |

|   | 17/11                         | Incest        |                      | TMOLET 1999       |                  |                    |    |

#### **U2** Parameters Setup

- 1. Select to highlight nets DM1 DQS1\_N under U2 .

- 2. Click the icon 토 in the field of **I/O Selection** column and select **Input** from the drop-down list.

- 3. Assign the nets **DM1 DQ15** with the **Receiver IO Model DQ\_34\_ODT60\_1333** from the drop-down list.

- 4. Assign the nets **DQS1\_P DQS1\_N** with **Receiver IO Model DQS\_34\_ODT60\_1333** from the drop-down list.

| Comp<br>NetNa | PinName/NetName(Sor | 1/O Selection | Transmitter IO Model | Receiver IO Model | Stimulus Pattern | Stimulus Offset(s) | Tut . |

|---------------|---------------------|---------------|----------------------|-------------------|------------------|--------------------|-------|

| ⊕             | F7/CLK_P            | Input         |                      | CLKIN_1333        |                  |                    |       |

| -             | G7/CLK_N            | Input         |                      | CLKIN_1333        |                  |                    |       |

|               | H2/CS_B             | Input         |                      | INPUT_1333        |                  |                    |       |

|               | 87/DM1              | Input         |                      | DQS_34_ODT60_1333 |                  |                    |       |

|               | 83/DQ8              | Input         |                      | DQS_34_ODT60_1333 |                  |                    |       |