Altıum.

# 只读存储器ROM-FLASH

Altıum.

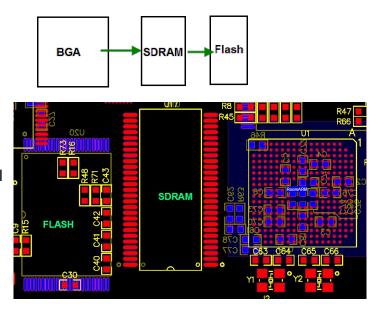

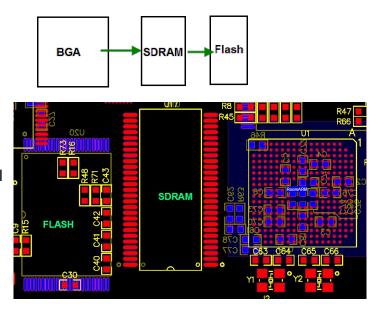

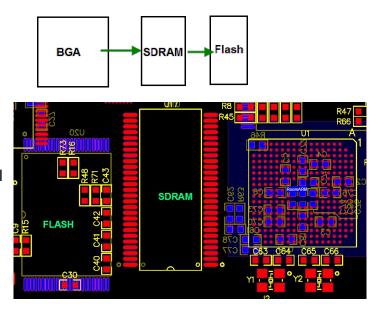

- ➤ FLASH特点

- ▶ 速率较低,通常在50Mhz以下

- ▶ 静态存储

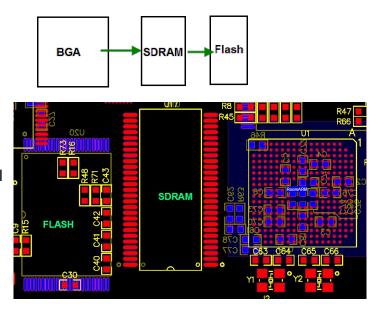

- > 布局

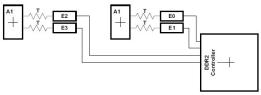

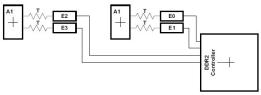

- > 一般采用菊花链

- > Flash和SDRAM的推荐距离为500-1000mil

# 只读存储器ROM-FLASH

- > 特性阻抗:50欧

- > 线间距3W

- > 等长范围:+/-100mil

# 只读存储器ROM-EEPROM电路概述

### **EEPROM**

EEPROM(电可擦可编程只读存储器)这是一种具有可擦除功能,擦除后即可进行再编程的ROM内存,一种掉电后数据不丢失的存储芯片,EEPROM可以在电脑上或专用设备上擦除已有信息,重新编程。这类芯片一般用于即插即用。

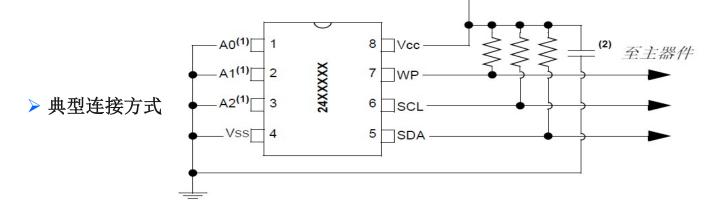

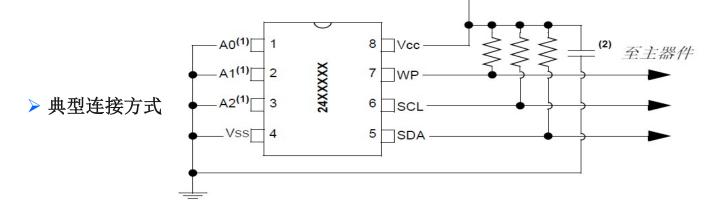

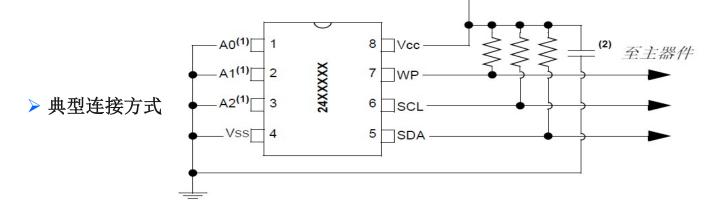

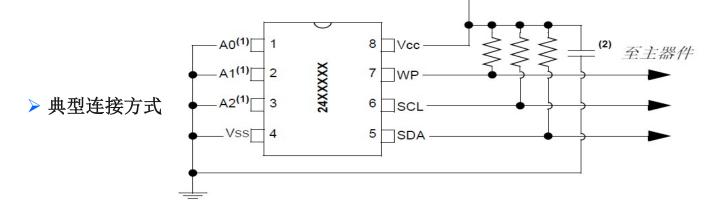

# 只读存储器ROM-EEPROM典型电路

Vcc

- 1.在某些器件中,引脚A0,A1,A2在内部未连接

- 2.应使用一个去耦合电容(通常为0.1UF)来帮助滤除VCC上的小纹波

# 只读存储器ROM-EEPROM典型电路

1.2.3: A0 A1 A2 器件地址选择

5: SDA 串行数据,地址

▶ 管脚定义 6: SCL 串行时钟

7: WP 写保护

8: VCC +1.8V~6.0V工作电压

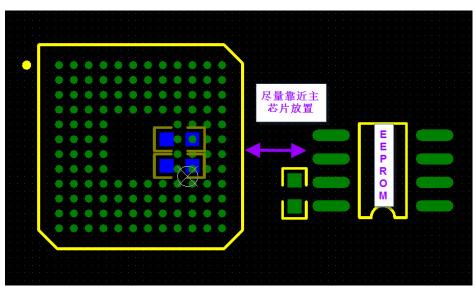

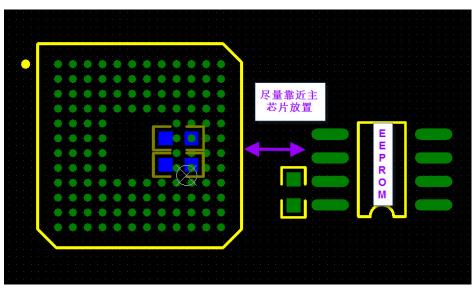

# 只读存储器ROM-EEPROM布局要求

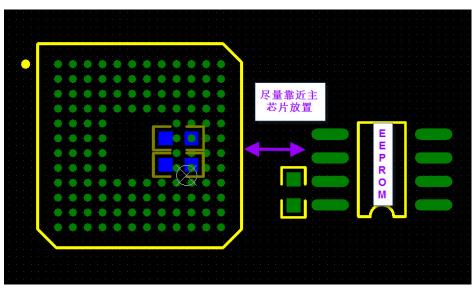

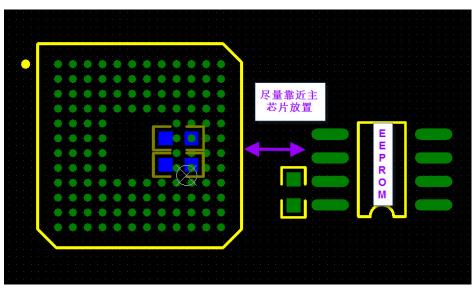

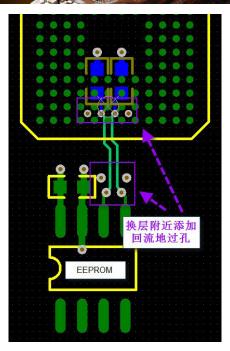

> 靠近主芯片放置,使距离尽量短

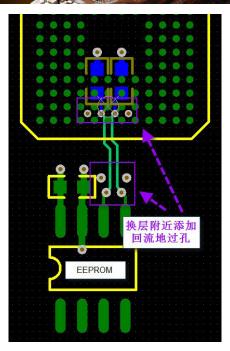

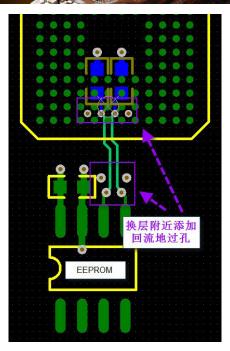

# 只读存储器ROM-EEPROM布线要求

### **EEPROM**电路布线要求

- (1) 控制50欧姆阻抗。

- (2) 两根线并行走,与其他信号线保持3W以上的间距。

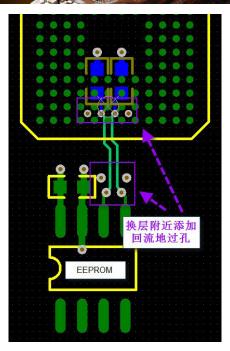

- (3) 尽量在表层走线;如需换层,需要有完整的参考平面,保持阻抗 连续性;并保证过孔数量不超过3个。

且在换层处100mil以内添加一个或者两个回流地孔。

# 随机存储器-动态RAM SDRAM

### > SDRAM (同步动态随机存储器)

### > 管脚定义解释

| 信号名。             | 功能描述。    |

|------------------|----------|

| CLK.             | 时钟。      |

| CKE.             | 时钟使能。    |

| CS#.             | 片选。      |

| WE#.             | 读写。      |

| RAS#.            | 列选。      |

| CAS#.            | 行选。      |

| DQM <sub>e</sub> | 数据掩码。    |

| BAO, BA1.        | Bank 选择。 |

| A 0-A11.         | 地址。      |

| DQ 0-DQ 15.      | 数据(输出)。  |

| VDDQ.            | DQ 电源。   |

| VSSQ.            | DQ 地。    |

| VDD.             | 电源。      |

| VSS.             | 地。       |

# 随机存储器-动态RAM SDRAM

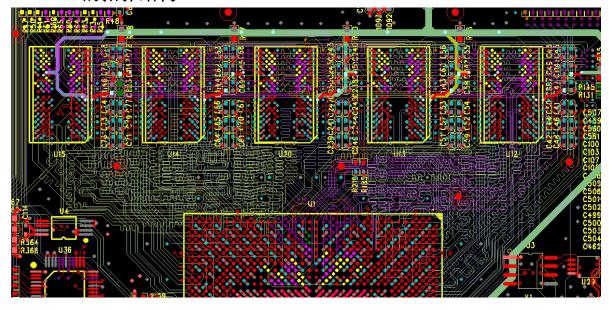

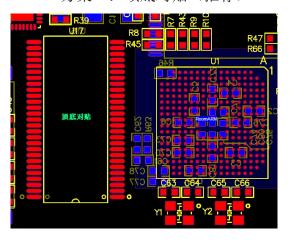

- ➤ SDRAM的布局原则: 靠近CPU放置

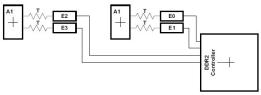

- > SDRAM X 1片时:点对点的布局方式

- > SDRAM到CPU的中心距离为:

当中间无排阻时: 900-1000mil 当中间有排阻时: 1000-1300mil

# 随机存储器-动态RAM SDRAM

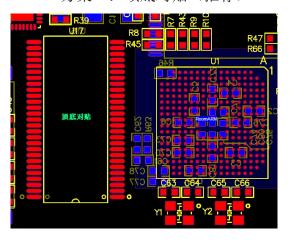

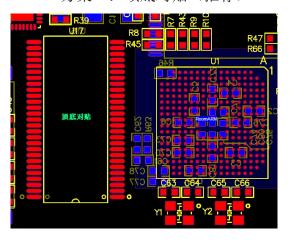

### ➤ SDRAM的布局原则:

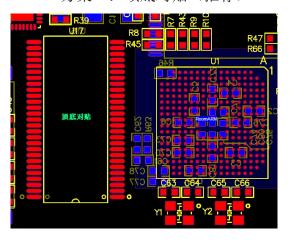

➤ SDRAM X 2片时:相对于CPU严格对称

方案一: 顶底对贴(推荐)

方案二:与CPU放在同一面

# 随机存储器-动态RAM SDRAM

# Altium.

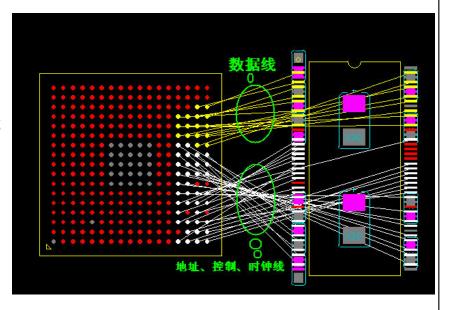

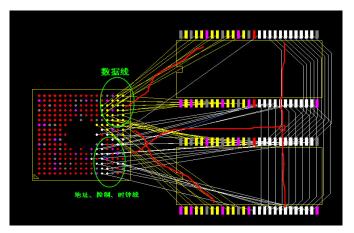

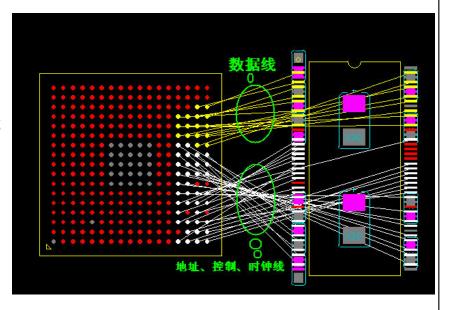

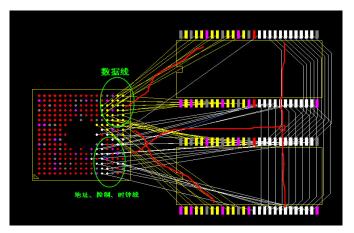

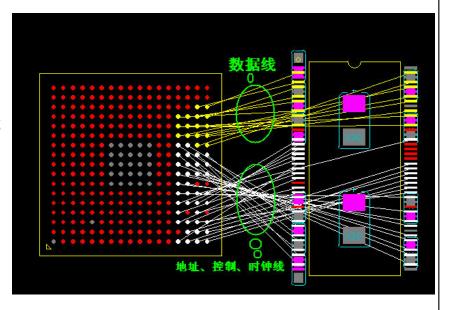

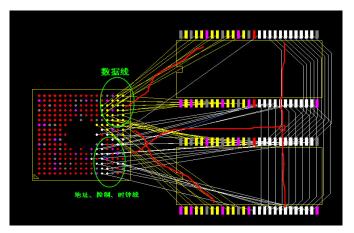

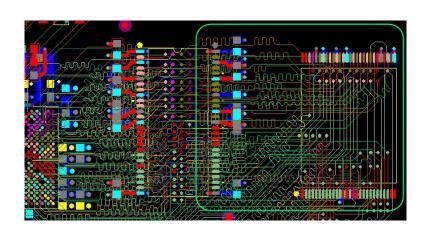

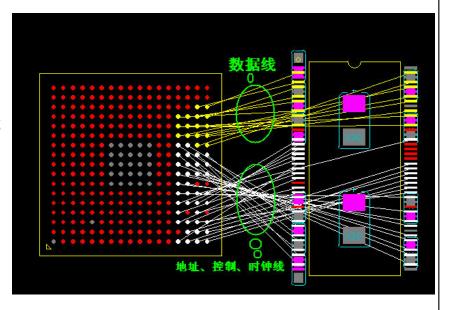

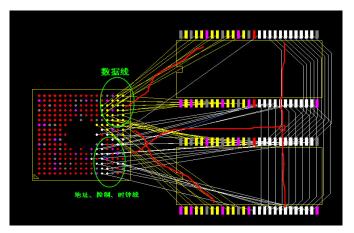

### > SDRAM的布线

- > 特性阻抗:50欧姆

- ▶ 数据线每9根尽量走在同一层(D0~D7,LDQM;D8~D15,HDQM)

- > 数据线、地址(控制)线、时钟线之间的距离保持20mil以上或至少3W

- ➢ 空间允许的情况下,应该在它们走线之间加一根地线进行隔离。地线宽度推荐为15-30mil

- > 完整的参考平面

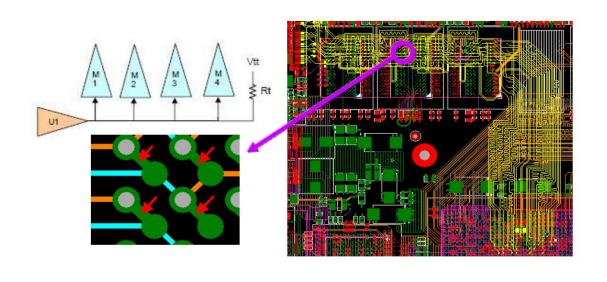

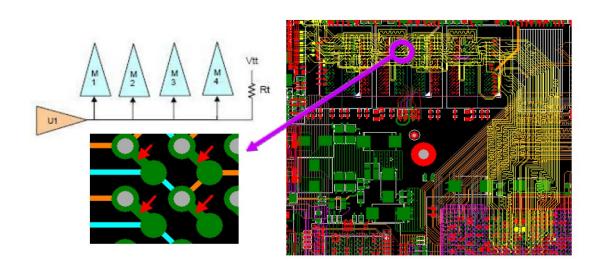

- ➤ 布线拓扑结构(默认采用远端分支)-T点(过孔)打在两片SDRAM中间

# Altium. 随机存储器-动态RAM SDRAM > SDRAM的拓扑结构 远端分支(星形/T形) 菊花链 - 地址控制线 • 地址控制线 - 数据线时钟线 数据线时钟线

# 随机存储器-动态RAM SDRAM

- >SDRAM的等长布线

- > Class规则:

将所有数据线设为sdram\_data\_bus; 地址线,控制线,时钟线设为sdram\_addr\_bus

> 等长规则:

所有信号线参照时钟线的长度等长

> 误差范围:

数据线误差范围控制在+/- 50mil 地址线误差范围控制在+/- 100mil

Altıum.

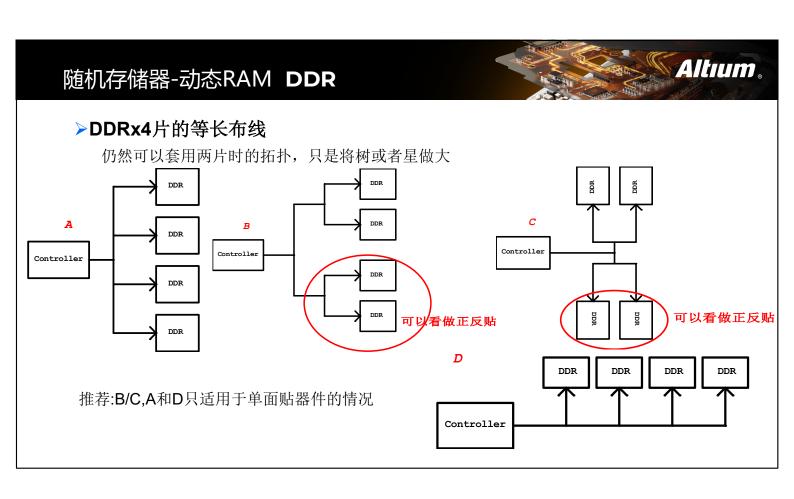

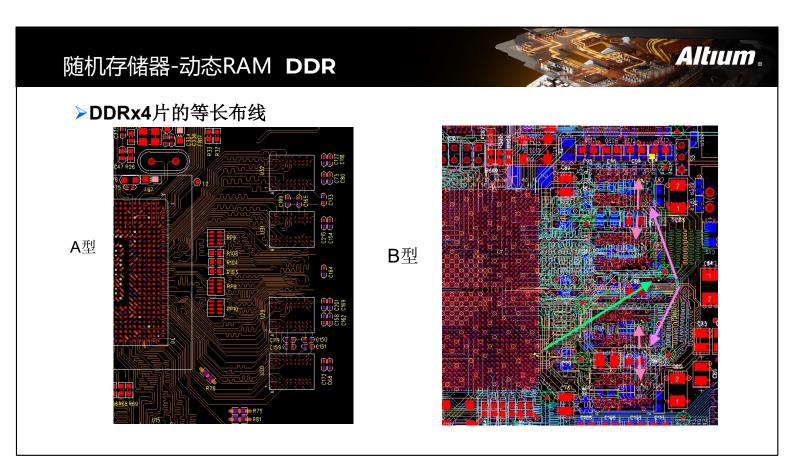

# 随机存储器-动态RAM DDR

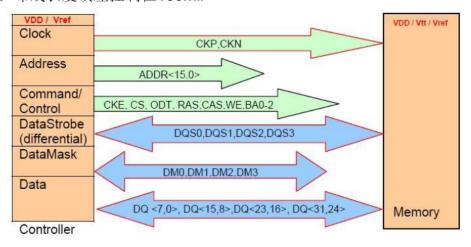

### >DDR的设计

管脚定义解释

| 管脚数₽            | 信号名。            | 功能描述。            | ¢3  |

|-----------------|-----------------|------------------|-----|

| 20              | CK, CK#         | 全局时钟输入。₽         | ÷   |

| 10              | CKE.            | 时钟使能信号输入。。       | t)  |

| 10              | CS#ø            | 片选信号输入。₽         | 4J  |

| 3₽              | RAS#, CAS#, WE# | 命令信号输入。₽         | 47  |

| 20              | LDM, UDM        | 数据 mask 信号输入。₽   | 42  |

| 13*₽            | A<012>+         | 地址信号输入。。         | 47. |

| 2₽              | BA0, BA1        | BANK 选择信号输入。。    | 42  |

| 16*₽            | DQ<015>@        | 数据信号输入/输出。₽      | φ   |

| 2₽              | LDQS, UDQS      | 数据锁存信号输入/输出。↩    | 47  |

| 5* <sub>0</sub> | NC.             | 空引脚。。            | 47  |

| 2₽              | DNU₽            | 不使用引脚。 🗸         | 47  |

| 5₽              | VDDQ₽           | DQ 电源电压 (2.5V)。₽ | 47  |

| 5₽              | VSSQ₽           | DQ 地。→           | 47  |

| 3≠              | VDDø            | 器件电源电压 (2.5V)。↓  | 47  |

| 3≠              | VSS.            | 器件地。。            | 47  |

| 1₽              | VREF₽           | SSTL_2 参考电压。₽    | 47  |

DDR SDRAM 封装结构图+

DDR SDRAM 管脚功能说明。

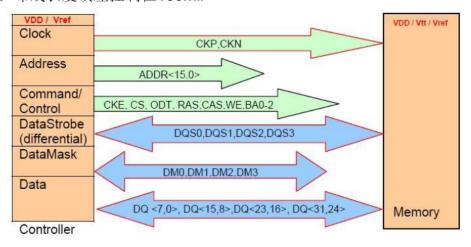

# 随机存储器-动态RAM DDR

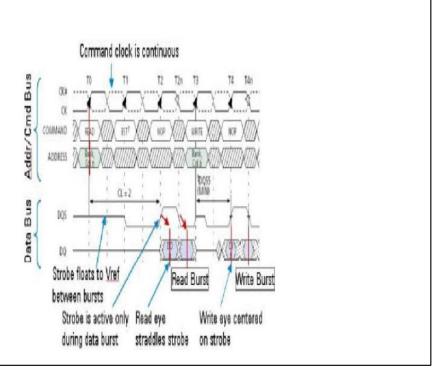

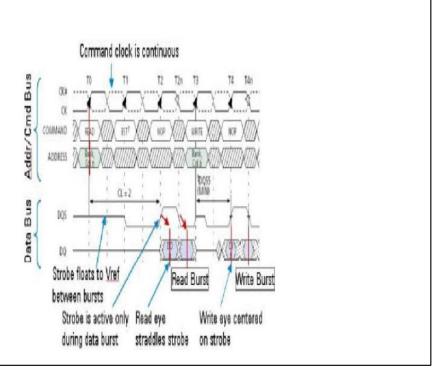

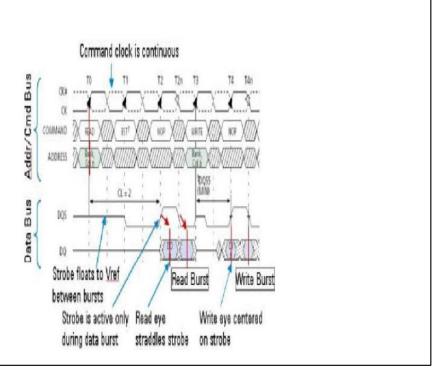

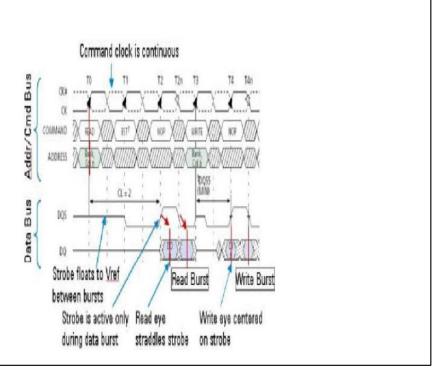

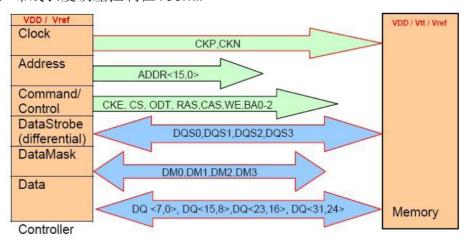

- ❖ 工作原理:

- 一. DDR的读写操作时序如图 所示。图中,命令信号与 地址信号参考CK信号上升 沿输入到DDR。

- 二. 读数据时DQ随着DQS并参考DQS信号沿输出,写数据时DQ随着DQS并参考DQS的信号沿输入,读写数据时DQS都是双沿有效。

- 三. 读数据时,输出的DQS由 送入DDR的差分时钟 CK/CK#使用DDR存储器 中的一个DLL生成DQS, 并使之与输出数据对齐。

- 四. 虽然DDR存储器不用差分 输入时钟来发送或接收数 据,但是所用DQS信号与 输入时钟的频率有关。

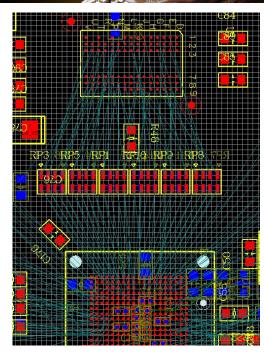

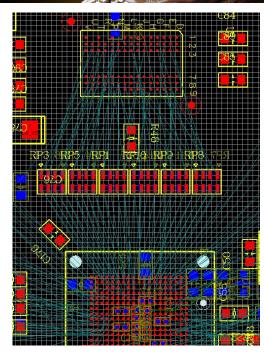

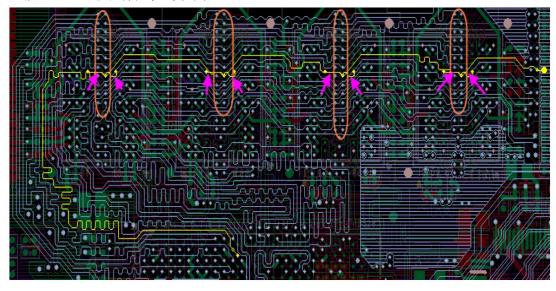

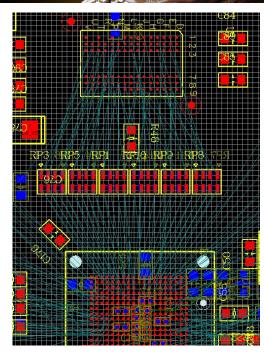

- ➤ DDR的布局

- ▶ 布局原则是:靠近CPU摆放

- ▶ DDRx1片时,点对点的布局方式

- ▶ DDR到CPU推荐的中心距离:

当中间无排阻时: 900-1000mil

当中间有排阻时: 1000-1300mil

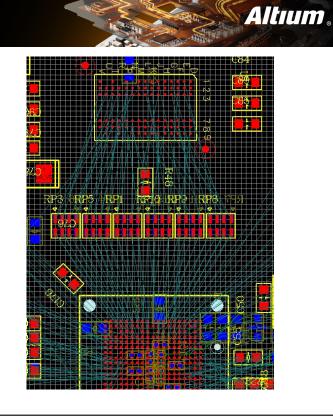

# 随机存储器-动态RAM DDR DDR的布局 DDRx2片时,相对于CPU严格对称 X < 1660mil Y1 = Y2 < 650mil VREF电容的位置 VREF电容的位置

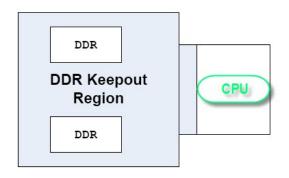

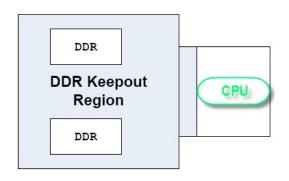

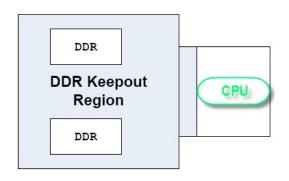

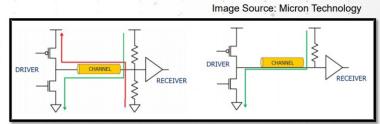

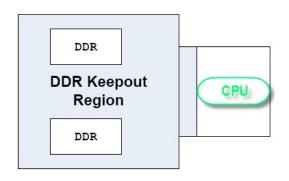

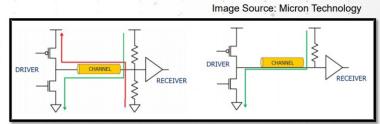

### >DDR保护区域

DDR2 保护区域 (Keepout Region): DDR2 内存组,所有同 DDR 相关的阻容电路,一直向 CPU 方向延伸至 CPU 的 DDR 控制器,称为 DDR 保护区域(DDR Keepout Region)。这个区域里需满足以下条件:

- a) 不得出现与 DDR 无关的信号。

- b) 必须提供完整的地平面(信号线下方地平面不得中断)。

- c) 必须提供完整的 VCC\_1V8 电源平面 (信号线下方电源平面不得中断)。

# 随机存储器-动态RAM DDR

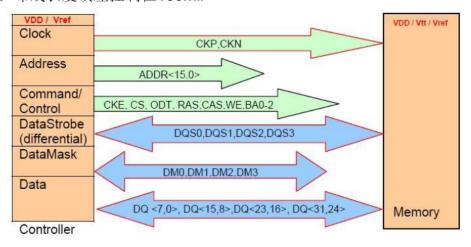

- > 特性阻抗:单端50欧,差分100欧

- ▶ 数据线每10根尽量走在同一层 (D0~D7,LDM,LDQS)(D8~D15,UDM,UDQS)

- ➤ 信号线的间距满足3W原则

### **▶DDR的布线**

- ▶ 数据线、地址(控制)线、时钟线之间的距离保持20mil以上或至少3W

- > 完整的参考平面

- ▶ VREF电源走线推荐>=20~30mil

- ▶ 误差范围: 差分对误差严格控制在5mil 数据线误差范围控制在+/- 25mil 地址线误差范围控制在+/- 100mil

### ▶Class规则

将数据类设为2组Class(D0~D7,LDM,LDQS)(D8~D15,UDM,UDQS); 地址线,控制线,时钟线设为1组Class

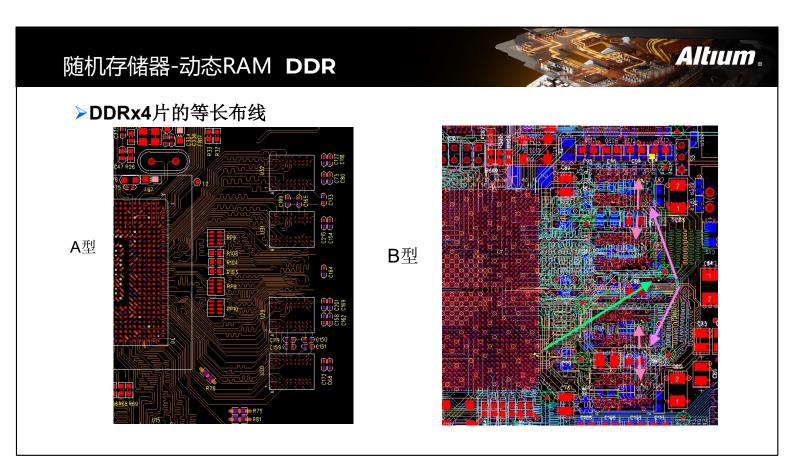

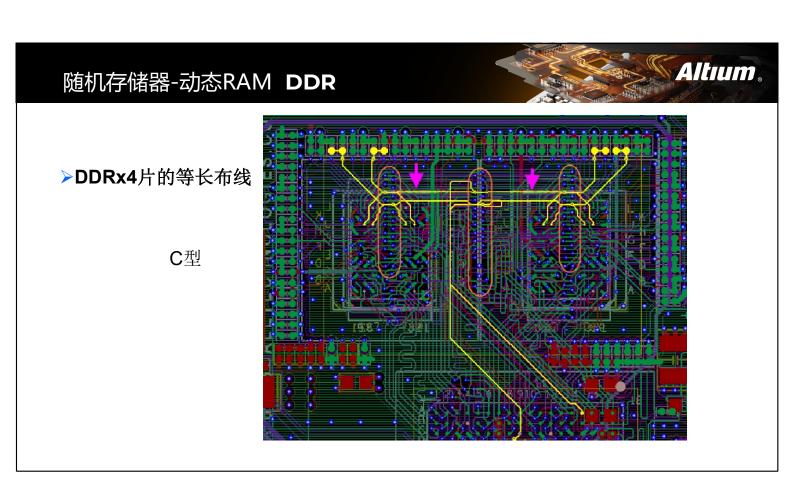

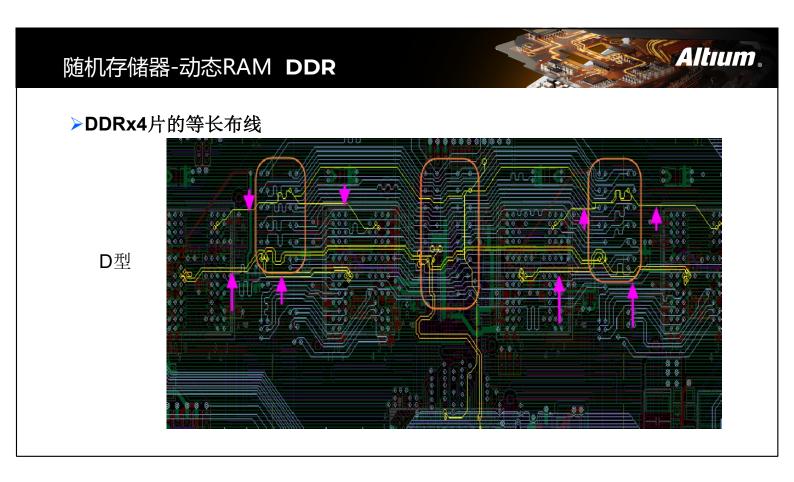

### ▶DDRx1片的等长布线

### >等长规则:

所有信号线参照时钟线的长度等长

### ▶误差范围:

数据线误差范围控制在+/- 25mil 地址线误差范围控制在+/- 100mil

###

# >DDR的时序设计

▶DDR(采用树形或者星型拓扑)

| DQSL/DQ<br>SH<br>DQ0~DQ1<br>6<br>DQML/DQ<br>MH | 严格等长设计,误差控制在±2  | 25mil |        |

|------------------------------------------------|-----------------|-------|--------|

| CLK/CLK#                                       | 严格差分等长设计        |       | 尽量控制等长 |

| A0~A11                                         |                 |       |        |

| WE/CAS/R<br>AS                                 |                 |       |        |

| BA0/BA1                                        | 等长设计,控制在±100mil |       |        |

| CS#                                            |                 |       |        |

| CKE                                            |                 |       |        |

# 随机存储器-动态RAM DDR2

>DDR VS DDR2

| Memory Type        | DDR                                                   | DDR2                                     |

|--------------------|-------------------------------------------------------|------------------------------------------|

| Core Voltage(VDD)  | 2.5V                                                  | 1.8V                                     |

| I/O Voltage (VDDQ) | SSTL_2(2.5V)                                          | SSTL_1.8(1.8)                            |

| Data Rate          | 200/266/333/400Mbps                                   | 400/533/667/800Mbps                      |

| Bus Frequency      | 100/133/166/200MHz                                    | 200/266/333/400MHz                       |

| Core Frequency     | 100/133/166/200MHz                                    | 100/133/166/200MHz                       |

| Pre-fetch          | 2-bit                                                 | 4-bit                                    |

| Burst Length       | 2/4/8                                                 | 4/8                                      |

| Data Strobe        | Single DQS                                            | Differential DQS, /DQS                   |

| Write Latency      | 1 clock                                               | (Read Latency-1) clock                   |

| CAS Latency        | 1.5, 2, 2.5                                           | 3, 4, 5                                  |

| Package            | x4/x8/x16: 66-pin TSOP(II)<br>x4/x8/x16: 60-ball FBGA | x4/x8: 60 ball FBGA<br>x16: 84 ball FBGA |

| New Features       |                                                       | OCD<br>ODT<br>Posted CAS                 |

DDD ve DDD2

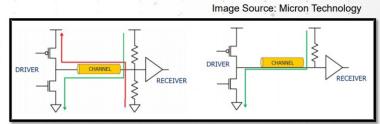

### Altium 随机存储器-动态RAM DDR2 SDRAM Data Bus DDR SDRAM SDR SDRAM DDR2 Array SDRAM Prefetch 4 bit 2 bit 1 bit DDR I Đạta Freg = 200 MH >DDR VS DDR2 100MHz 100MHz 100MHz Internal bus operating Memory frequency Data Bus 100MHz External clock 200MHz 100MHz Array Buffers frequency Data bus 400Mbps 200Mbps 100Mbps DDR II speed min min Data Bus Buffers Array

# 随机存储器-动态RAM DDR2

### ▶DDR2的设计

▶DDR新特性:

DDR2可以看做DDR的升级,由于DDR的内部设计使得I/O口的速率最高只能达到200Mhz,而DDR2最高可以提高到400Mhz,也就是DDR2比DDR提高了一倍的速率。在信号管脚上变化的主要是将单端的DQS信号变成了差分的DQS和DQS#。

DQS DQS/DQS#

Clock Frequency

200MHZ(Max) 400MHZ(Max)

- ▶DDR2的布局

- ▶ 布局思路同DDR

# 随机存储器-动态RAM DDR2

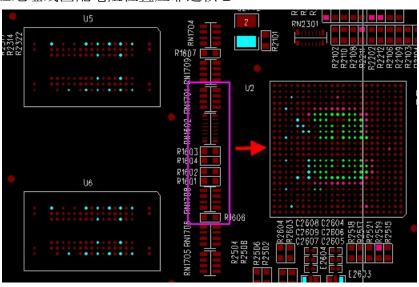

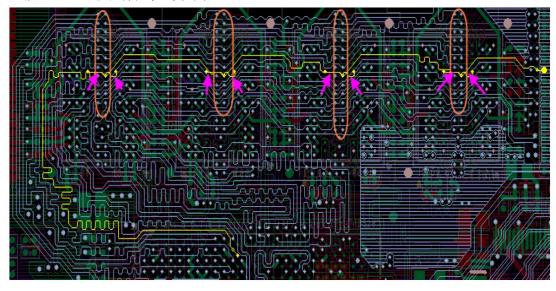

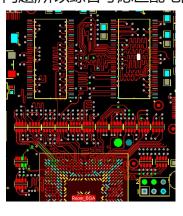

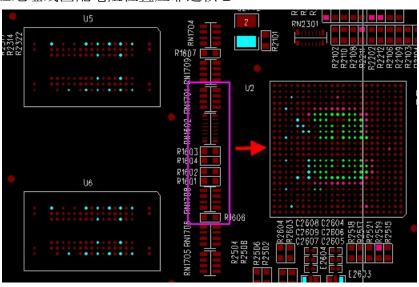

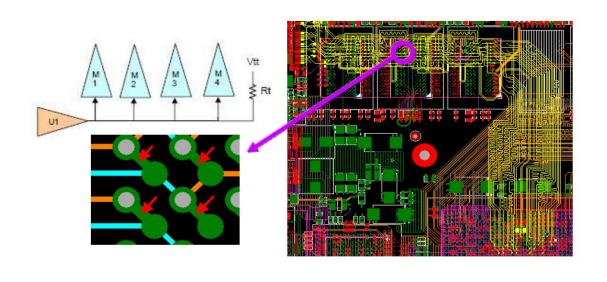

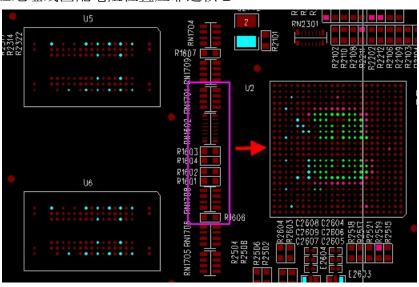

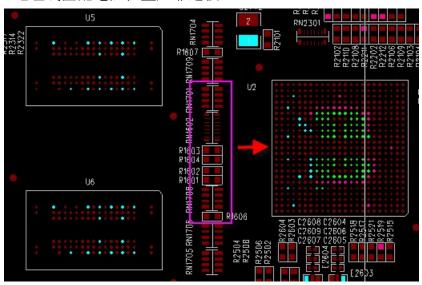

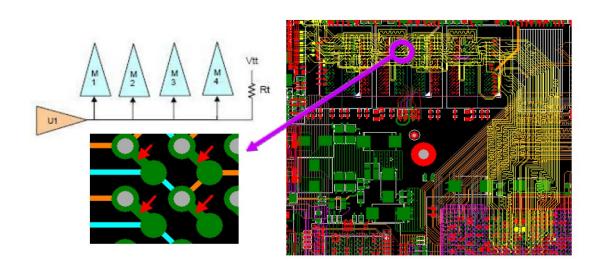

## ▶DDR2数据匹配电阻的布局

>数据匹配电阻应靠近DDR.布线也会容易些。 (数据线是双向传输的,有的核芯不一定有 ODT功能.如有ODT功能匹配电阻放那边都没有 问题,当核芯没有ODT功能匹配电阻靠CPU就有 问题,所以综合考虑匹配电阻应靠DDR放置)

左图SDRAM的数 据线排阻应近 SDRAM直接接上 可以减少过孔.

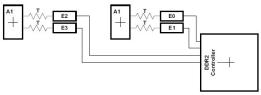

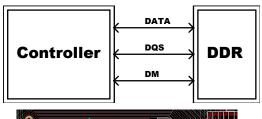

Figure 8-11 shows the topology and routing for the DQS and DQ net classes; the routes are point to point. Skew matching across bytes is not needed nor recommended.

Figure 8-11. DQS and DQ Routing and Toplogy

Table 8-12. DQS and DQ Routing Specification

| NO. | PARAMETER                                               | MIN     | TYP  | MAX     | UNIT |

|-----|---------------------------------------------------------|---------|------|---------|------|

| 1   | Center-to-center DQS-DQSn spacing in E0 E1 E2 E3        |         |      | 2w      | 1    |

| 2   | DQS-DQSn skew in E0 E1 E2 E3                            |         |      | 25      | Mils |

| 3   | Center-to-center DQS to other DDR2 trace spacing (1)    | 4w      |      |         |      |

| 4   | DQS/DQ nominal trace length (2)(3)(4)                   | DQLM-50 | DQLM | DQLM+50 | Mils |

| 5   | DQ-to-DQS skew length mismatch <sup>(2)(3)(4)</sup>     |         |      | 100     | Mils |

| 6   | DQ-to-DQ skew length mismatch <sup>(2)(3)(4)</sup>      |         |      | 100     | Mils |

| 7   | DQ-to-DQ/DQS via count mismatch <sup>(2)(3)(4)</sup>    |         |      | 1       | Vias |

| 8   | Center-to-center DQ to other DDR2 trace spacing (1)(5)  | 4w      |      |         |      |

| 9   | Center-to-center DQ to other DQ trace spacing (1)(6)(7) | 3w      |      |         |      |

| 10  | DQ/DQS E skew length mismatch (2)(3)(4)                 |         |      | 100     | Mils |

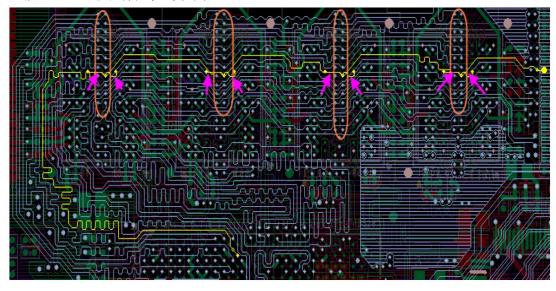

### ▶DDR2地址线匹配电阻的布局

▶DDR2地址线匹配电阻位置应靠近核芯

# 随机存储器-动态RAM DDR2

### ▶DDR2的布线

- ▶ 特性阻抗:单端50欧,差分100欧

- ▶ 数据线每11根尽量走在同一层

(D0~D7, DQM0,DQS0 N,DQS0 P)

(D8~D15, DQM1,DQS1 N,DQS1 P)

(D16~D23,DQM2,DQS2\_N,DQS2\_P)

(D24~D31,DQM3,DQS3 N,DQS3 P)

DDR2x1片

❖ 误差范围:

差分对误差严格控制在5mil 数据线误差范围控制在+/-15mil 地址线误差范围控制在+/-100mil

DDR2x2片

➤ 信号线的间距满足3W原则

- ▶ 数据线、地址(控制)线、时钟线之间的距离保持20mil以上或至少3W

- > 完整的参考平面

- ▶ VREF电源走线推荐>=20~30mil

### ▶DDR2的布线

- ▶ DQGATE组分为低16位和高16位

- DQGATE\_L = DDRCLKOUTP + (DDRDQSOP + DDRDQS1P) / 2

- ▶ 布线拓扑: 布线长度误差控制在100mil

- DQGATE\_H = DDRCLKOUTP + (DDRDQS2P + DDRDQS3P) / 2

# 随机存储器-动态RAM DDR2

### DDR2 (采用树形或者星型拓扑)

### ▶DDR2芯片时序设计

| DQSH/DQS<br>H# | 严格差分等长设计                |                  |       |

|----------------|-------------------------|------------------|-------|

| DQSL/DQS<br>L# | 严格差分等长设计                | 严格等长设计,控制在±15mil |       |

| DQ0~DQ16       | 変数をレミルキ もをした            |                  |       |

| DQML/DQ<br>MH  | 严格等长设计,控制在<br>  ± 15mil |                  | 尽量控制等 |

| CLK/CLK#       | 严格差分等长设计                |                  | K     |

| A0~A11         |                         |                  |       |

| WE/CAS/RA<br>S | 等长设计,控制在                | <br>             |       |

| BA0/BA1        | ± 100mil                |                  |       |

| CS#            |                         |                  |       |

| CKE            |                         |                  |       |

### ▶DDR3的设计

▶ DDR3的新特性

DDR3和DDR2在信号定义上基本上是一样的,信号定义上变化很小,大家可以看到有些芯片上会出现两根新的信号TDQS/TDQS#,它只是在8位RAM上会使用到,4位和16位的RAM不会用到他们,所以我们这里不特别阐述,我们可以简单的把它看做单向传输的DQS信号(RAM->Controller),将其和DQS/DQS#,DATA,DM归为一组即可。

# 随机存储器-动态RAM DDR3

### ▶DDR3与DDR2的比较

| Technology                            | DDR2          | DDR3           |  |  |

|---------------------------------------|---------------|----------------|--|--|

| Max Clock Freq. (MHz)/Data rate(Mbps) | 533/1066      | 800/1600       |  |  |

| Power Requirement                     |               |                |  |  |

| VDD (Volts)                           | 1.8 +/- 0.1   | 1.5 +/- 0.075  |  |  |

| Vtt (Volts)                           | 0.9 +/- 0.04  | 0.75 +/- TBD   |  |  |

| Vref (Volts)                          | 0.9 +/- 0.018 | 0.75 +/- 0.015 |  |  |

| Input Thres                           | holds         |                |  |  |

| Vih/Vil (Volts)                       | 0.9 +/- 0.2   | 0.75 +/- 0.175 |  |  |

| Delay Matching Requirement            |               |                |  |  |

| Match ADDR/CMD/CNTRL to Clock tightly | Yes           | Yes            |  |  |

| Match DQ<7,0>, DM0 to DQS0 tightly    | Yes           | Yes            |  |  |

| Match DQ<15,8>, DM1 to DQS1 tightly   | Yes           | Yes            |  |  |

| Match DQ<22,16>, DM2 to DQS2 tightly  | Yes           | Yes            |  |  |

| Match DQ<31,23>, DM3 to DQS3 tightly  | Yes           | Yes            |  |  |

| Match DQS0-3 to Clock loosely         | Yes           | Not required   |  |  |

# Altium.

### ▶ DDR3与DDR、DDR2的比较

|                                   | DDR                      | DDR2                                | DDR3                                |

|-----------------------------------|--------------------------|-------------------------------------|-------------------------------------|

| 时钟频率                              | 100/133/166/200MHz       | 200/266/333/400MHz                  | 400/533/667/800MHz                  |

| <b>数据传输速率</b> 200/266/333/400Mbps |                          | 400/533/667/800Mbps                 | 800/1066/1333/1600Mbps              |

| <b>输入/输出位宽</b> x4/x8/x16/x32      |                          | x4/x8/x16                           | x4/x8/x16                           |

| 预取宽度                              | 2位                       | 4位                                  | 8位                                  |

| 突发长度                              | 2, 4, 8                  | 4, 8                                | 8                                   |

| 数据选通(DQS)                         | 单线                       | 单线/差分                               | 差分                                  |

| 电源电压                              | 2. 5V±0. 2V              | 1.8V±0.1V                           | 1.5V±0.075V                         |

| 接口类型                              | SSTL_25                  | SSTL_18                             | SSTL_15                             |

| CAS延迟(CL)                         | 2, 2.5, 3时钟频率            | 3, 4, 5时钟频率                         | 5, 6, 7, 8, 9, 10时钟频率               |

| 片内终结器(ODT)                        | 不支持                      | 支持                                  | 支持                                  |

| 封装类型                              | 66pin TSOP2<br>60pin BGA | 60pin BGA(x4, x8)<br>84pin BGA(x16) | 78pin BGA(x4, x8)<br>96pin BGA(x16) |

| Write Leveling                    | 不支持                      | 不支持                                 | 支持                                  |

### Altıum. 随机存储器-动态RAM DDR3 ▶DDR3的等长 ▶地址线长度要求 Table 8-24. CK and ADDR\_CTRL Routing Specification(1)(2) PARAMETER NO. MAX UNIT A1+A2 length 2500 mils A1+A2 skew A3 length 660 mils A3 skew<sup>(3</sup> 5 A3 skew<sup>(4)</sup> 125 mils A4 length 660 A4 skew AS length AS skew 100 10 AS+/AS- length 70 mils 11 AS+/AS- skew mils 12 AT length 500 mils 13 AT skew<sup>(6)</sup> mils 14 AT skew<sup>(7)</sup> CACLM-50 15 CK/ADDR\_CTRL nominal trace length<sup>(8)</sup> CACLM CACLM+50

# Altium

### ▶DDR3的等长

> 数据线长度要求

DDR3数据线以

DQS为基准25mil

There are four DQLMs, one for each byte (32-bit interface). Each DQLM is the longest Manhattan distance of the

byte; therefore: DQLM0 = DQLMX0 + DQLMY0 DQLM1 = DQLMX1 + DQLMY1 DQLM2 = DQLMX2 + DQLMY2 DQLM3 = DQLMX3 + DQLMY3

Table 8-25, Data Routing Specification (1)

| NO. | PARAMETER                                                 | MIN | TYP | MAX   | UNIT |

|-----|-----------------------------------------------------------|-----|-----|-------|------|

| 1   | DB0 nominal length <sup>(2)(3)</sup>                      |     |     | DQLM0 | mils |

| 2   | DB1 nominal length <sup>(2)(4)</sup>                      |     |     | DQLM1 | mils |

| 3   | DB2 nominal length <sup>(2)(5)</sup>                      |     |     | DQLM2 | mils |

| 4   | DB3 nominal length <sup>(2)(6)</sup>                      |     |     | DQLM3 | mils |

| 5   | DBn skew <sup>(7)</sup>                                   |     |     | 25    | mils |

| 6   | DQSn+ to DQSn- skew                                       | 99  |     | 5     | mils |

| 7   | DQSn to DBn skew <sup>(7)(8)</sup>                        |     | 25  | mils  |      |

| 8   | Center-to-center DBn to other DDR3 trace spacing (9)(10)  | 4w  |     |       |      |

| 9   | Center-to-center DBn to other DBn trace spacing (9)(11)   | 3w  |     | 30    |      |

| 10  | DQSn center-to-center spacing (12)                        | 9.0 |     | - 20  |      |

| 11  | DQSn center-to-center spacing to other net <sup>(9)</sup> | 4w  |     | (5)   |      |

- | DGSn center-to-center spacing to other nete\*\*

| External termination disallowed. Data termination should use built-in ODT functionality.

| DGLMn is the longest Manhattan distance of a byte. For definition, see Section 8.3.2.18.2 and Figure 8-39.

| DGLM0 is the longest Manhattan length for the net classes of Byte 0.

| DGLM1 is the longest Manhattan length for the net classes of Byte 1.

| DGLM2 is the longest Manhattan length for the net classes of Byte 2.

| DGLM3 is the longest Manhattan length for the net classes of Byte 2.

| DGLM3 is the longest Manhattan length for the net classes of Byte 2.

| DGLM3 is the longest Manhattan length for the net classes of Byte 3.

| Length matching is only done within a byte. Length matching across bytes is neither required nor recommer Each DGS pair is length matched to its associated byte.

| DGS pair is length matched to its associated byte.

| Center-to-center spacing is allowed to fall to minimum for up to 1.250 mils of routed length.

| Other DGR3 trace spacing means other DGR3 net classes not within the byte.

| DGS pair spacing is set to ensure proper differential impedance.

# 随机存储器-动态RAM DDR3

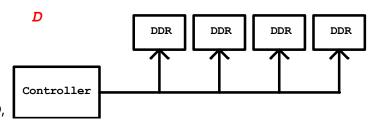

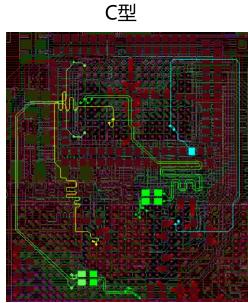

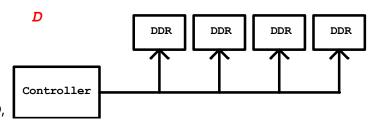

### ▶DDR3的拓扑结构

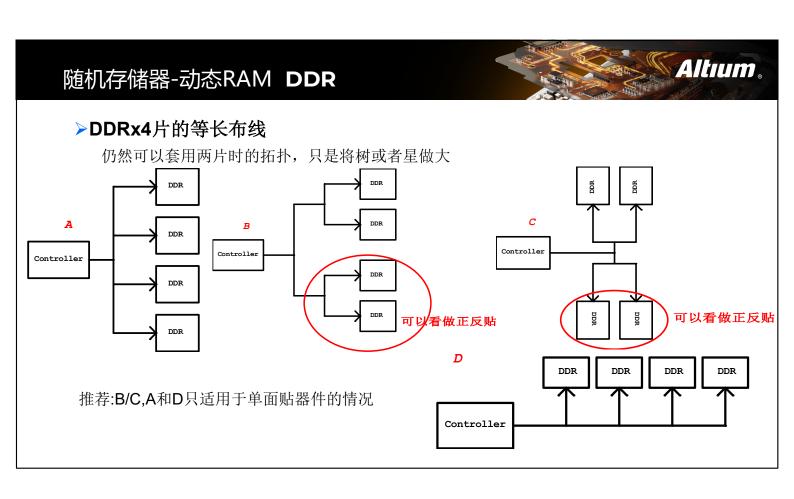

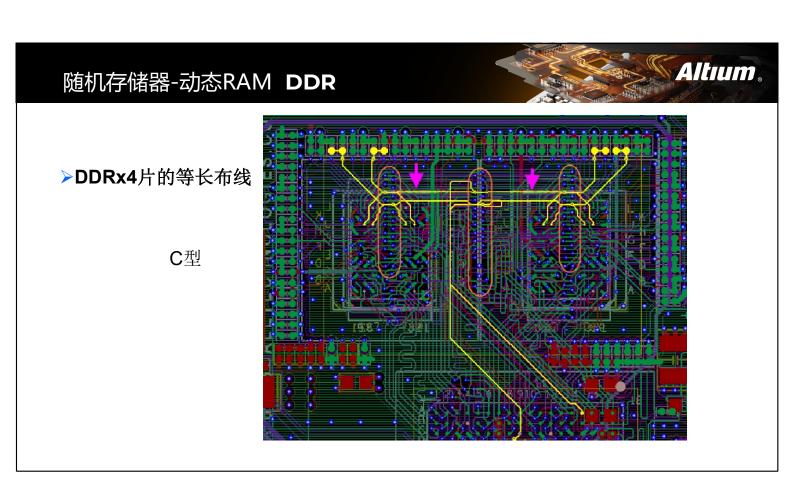

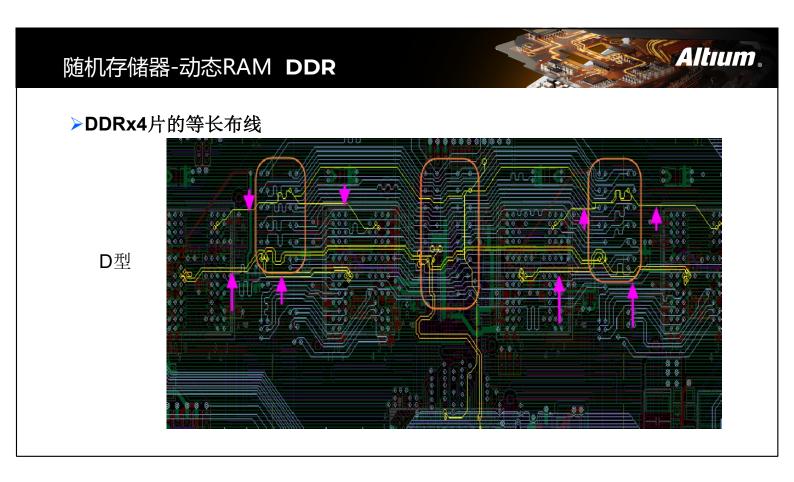

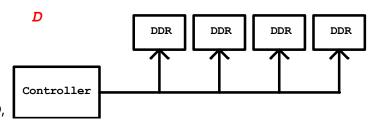

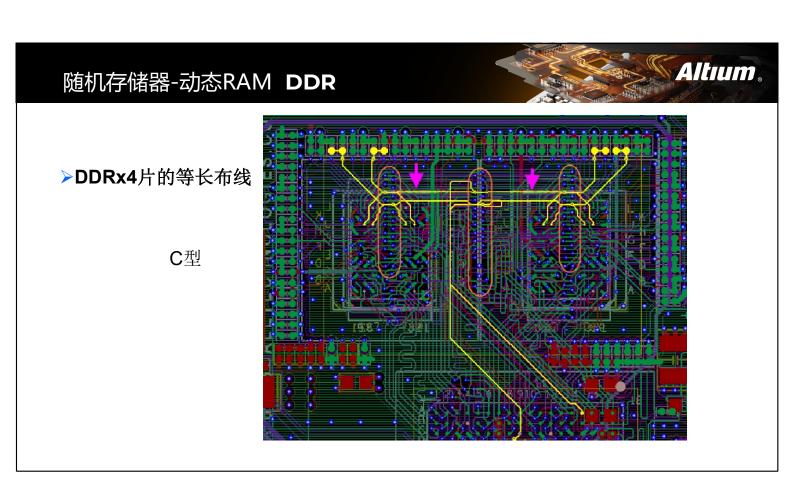

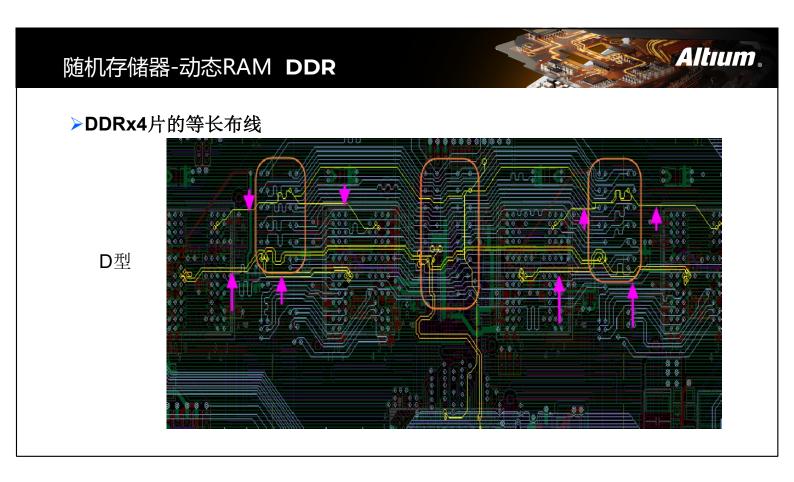

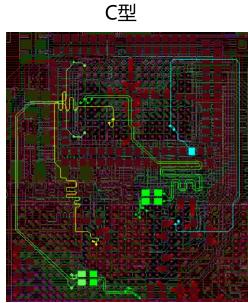

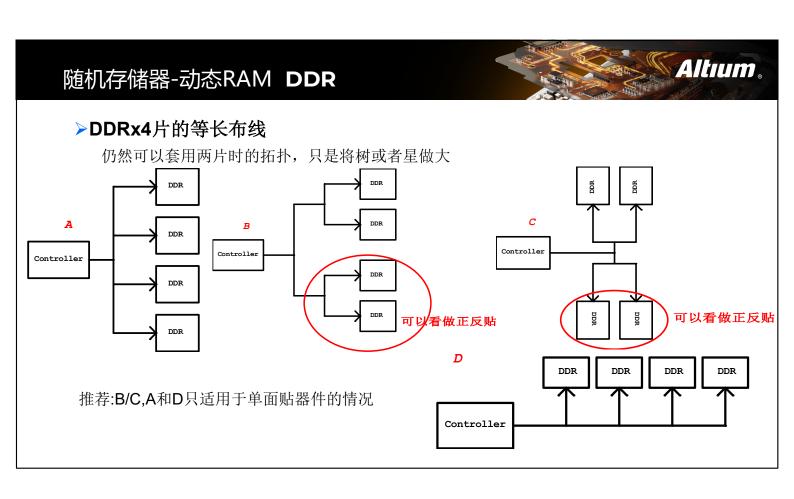

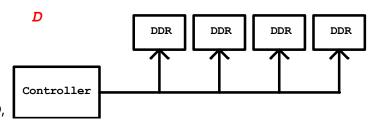

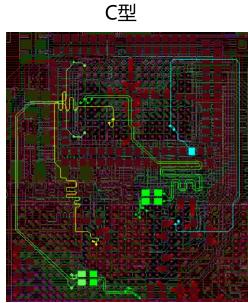

DDR3的地址拓扑和DDR2, DDR一样, 只是由 于其速率更高(最高可达到1.6Gbps), 所以除了 时序,信号完整性也成了我们需要关注的要点, 前文提到的在多片DDR设计时采用的4种拓扑, 我们在进行DDR3设计,尤其是当速率跑到 1.6Gbps时,通过仿真我们发现4种拓扑中只有D, 即菊花链拓扑满足信号完整件要求,但是这里并 不是说其他3种拓扑不适用,只是在满足时序要 求的情况下, D型拓扑能最好的达到信号完整件 的要求。

### ▶DDR3的拓扑结构

# 随机存储器-动态RAM DDR3

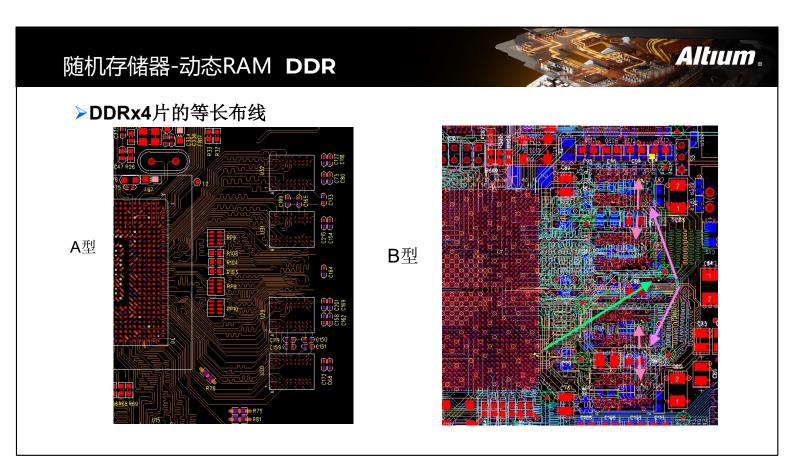

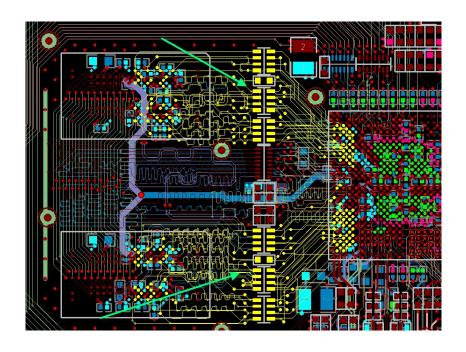

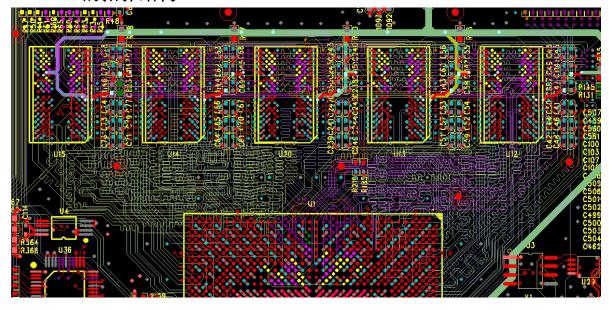

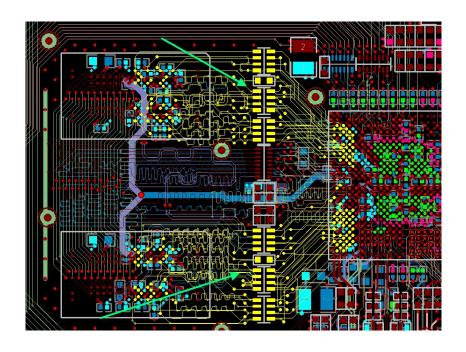

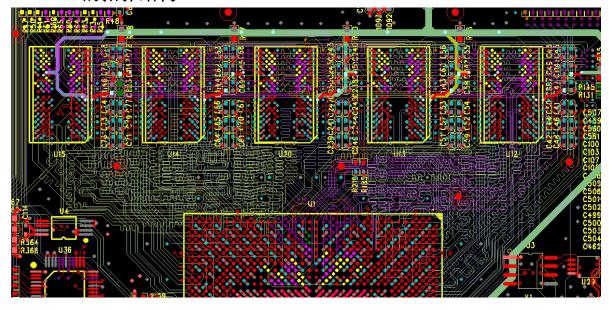

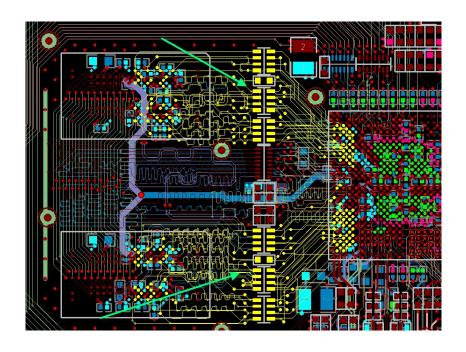

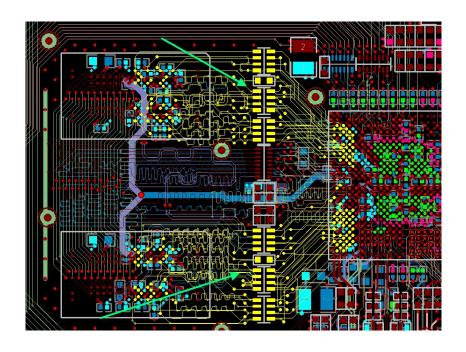

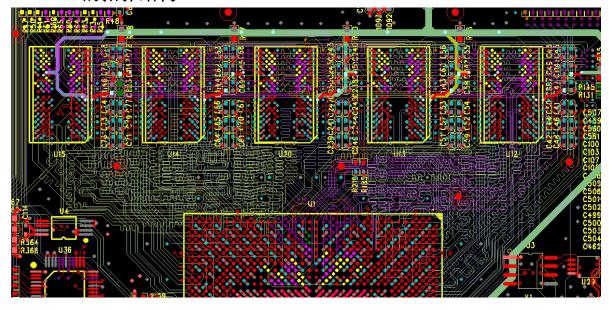

### ▶DDR3的布局布线实例

▶ 地址线布局布线要求优选F ly-By, 过孔到管脚长度尽量短, 长度在150mil左右

- ▶DDR3的布局布线实例

- ▶8颗DDR3正反对贴布线示例

# 随机存储器-动态RAM DDR3

- ▶DDR3芯片设计总结

- ▶DDR3(采用树形或菊花链拓扑)

| A0~A11     | J在士10mil                                |            | 尽量控制等<br>长 |

|------------|-----------------------------------------|------------|------------|

| RA0/RA1 制在 | 差分等长设计<br>控制等长,控<br>E±100mil如<br>菊花链拓扑则 | 尽量控制等<br>长 | X.         |

### DDR4新特点:

- 一. **8**位预读取,外部时钟频率是内部时钟频率的八倍,数据传输率最高可达**3**.**2**Gbps;

- 二. 内核电压仅为1.2V;

布局布线要求基本同DDR3:

等长要求(推荐以Layout Guide为准、以仿真结果为准):

- 一. 数据线最大长度尽量不超过2500mil,组内长度误差范围控制在+/-5mil,得益于Write Leveling技术,DQS与时钟线一般无长度误差要求,注意尽量查阅Layout Guide或datasheet,部分芯片会有组间、以及DQS与时钟线的等长要求;

- 二. 地址线误差范围控制在+/-20mil:

- 三. DQS、时钟差分对内误差范围控制在+/-3mil,设计阻抗时,使本对内间距不超过2倍线宽;

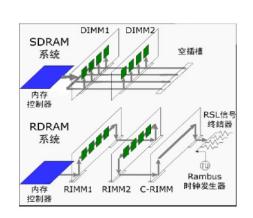

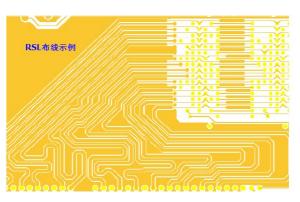

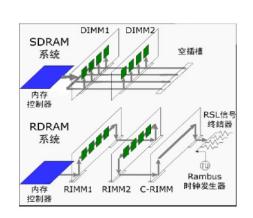

# 随机存储器-动态RAM RDRAM

- ➤ RDRAM是由R ambus公司推出的一种采用双沿触发技术的内存,有16/18bit (ECC)两种规格,能在很高的频率范围内通过一个简单的总线传输数据

- > 功能管脚说明

| 信号名                       | 类型    | 电平   | 功能描述                                                        |

|---------------------------|-------|------|-------------------------------------------------------------|

| DQA (8: 0)                | 10    | RSL  | 数据字节 A。在通道与 RDRAM 器件间进行一个字节的数据信号传递。在 x16 的系統中 DQA (8) 将不使用。 |

| DQB (8: 0)                | 10    | RSL  | 数据字节 B。在通道与 RDRAM 器件间进行一个字节的数据信号传递。在 x16 的系統中 DQB(8) 将不使用。  |

| RQ (7: 5) 或<br>ROW (2: 0) | Input | RSL  | 行访问控制。传递行访问的控制与地址信号。                                        |

| RQ (4: 0) 或<br>COL (4: 0) | Input | RSL  | 行访问控制。传递行访问的控制与地址信号。                                        |

| CFM, CFMN                 | Input | RSL  | Clock From Master。从通道中接收 RSL 信号的差分接口时钟。                     |

| CTM, CTM#                 | Input | RSL  | Clock To Master。发送 RSL 信号到通道的差分接口时钟。                        |

| CMD                       | Input | CMOS | 串行命令输入。与 SI00 和 SI01 一起用于读写控制寄存器, 也用于电源管理。                  |

| SCK                       | Input | CMOS | 串行时钟输入。用于读写 RDRAM 控制寄存器的时钟源。                                |

| SI01, SI00                | 10    | CMOS | 串行輸入輸出。通过串行协议读写控制寄存器,也用于<br>电源管理。                           |

| Vref                      |       | DC   | RSL 信号的逻辑门限参考电压。                                            |

| Vcmos                     |       | DC   | CMOS 输入输出管脚的电源电压。                                           |

| Vdda                      |       | DC   | RDRAM 模拟电路的电源电压。                                            |

| Vdd                       |       | DC   | RDRAM 内核与接口逻辑的电源电压。                                         |

| GNDa                      |       | DC   | RDRAM 模拟电路的地参考。                                             |

| GND                       |       | DC   | RDRAM 内核与接口逻辑的地参考。                                          |

# 随机存储器-动态RAM RDRAM

Altıum.

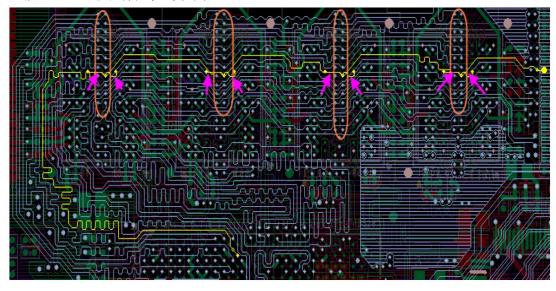

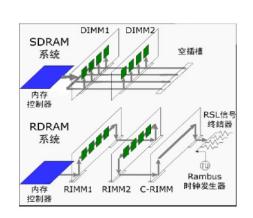

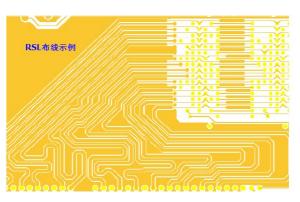

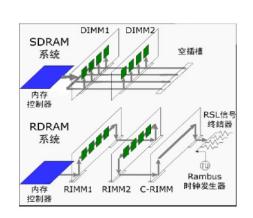

➤ RDRAM与 SDRAM架构 比较

### 特点:

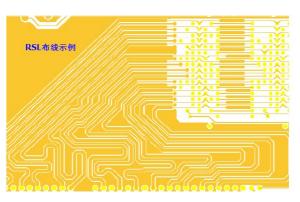

- 1.信号线数目较少,所有信号均为串联接法;

- 2.工作频率极高, 所有RSL电平信号都要包地, 并以地平面为参考:

- 3.DQ、RQ、和CTM、SCK、CMD等信号的走线长度在分段过程中每一段的长度都必须匹配,匹配的计算不仅包括走线,还句括管脚长度,误差挖制在+/-10mi1以内;

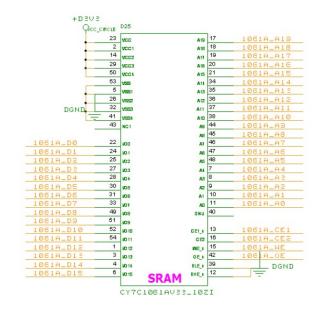

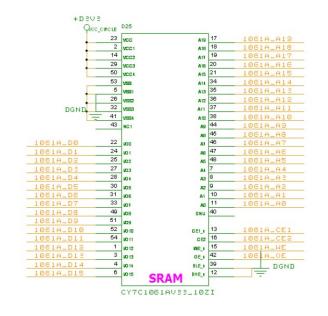

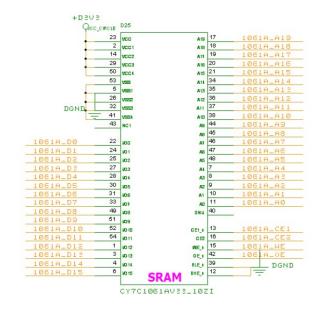

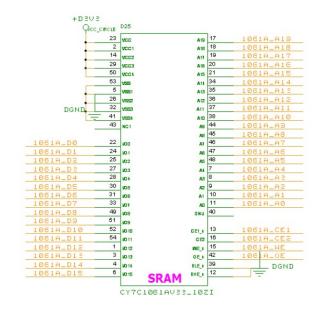

# 随机存储器-静态RAM SRAM

### > SRAM的特点

- >SRAM是Static RAM缩写,即静态随机存储器,它是一种具有静止存取功能的内存,不需要刷新电路就能保持内部存储数据的有效性,但断电后,数据仍然会丢失

- ▶SRAM存取速度快,但比相同容量的DRAM体积大,功耗也大,因此目前 单片SRAM容量一般都是几百K到几十M

# 随机存储器-静态RAM SRAM

### **▶SRAM**的特点

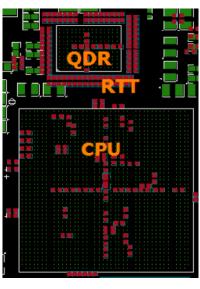

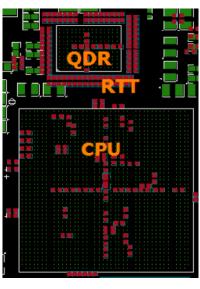

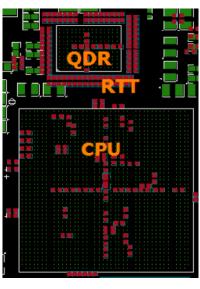

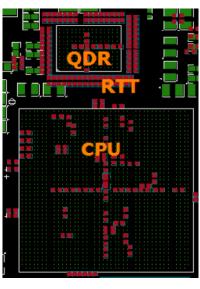

➤右图为SRAM,目前 SRAM运用较为广泛的是 QDR SRAM系列

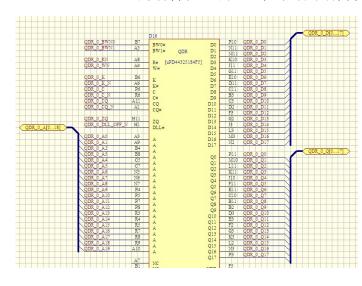

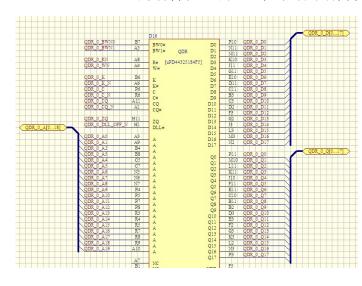

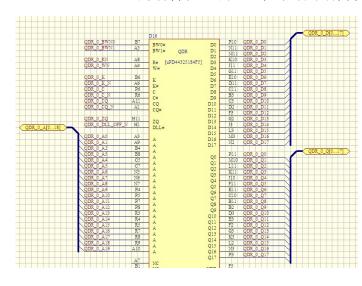

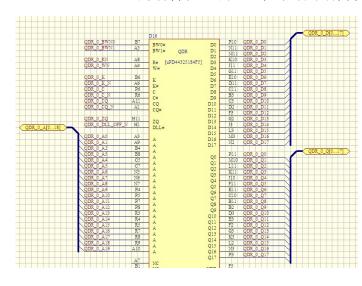

# 随机存储器-静态RAM QDR

# ➤ QDR的设计

▶ QDR的新特性: 可在一个时钟周期内传送四次数据(两次读与两次写数据)

| 信号名。                    | 功能描述。                     |

|-------------------------|---------------------------|

| К, К#                   | 输入时钟。。                    |

| C, C#0                  | 用于输出数据的输入时钟。。             |

| SA <sub>e</sub>         | 地址信号输入。。                  |

| D0-17 (35) o            | 数据信号输入。。                  |

| Q0-17 (35) <sub>o</sub> | 数据信号输出。*                  |

| ₩# <sub>\$</sub>        | 写操作控制信号。。                 |

| R#.                     | 读操作控制信号。。                 |

| BW0#- BW 1 (3) #.       | 字节写控制信号。。                 |

| Vref.                   | 输入参考电平。。                  |

| ZQ <sub>e</sub>         | 输出驱动器阻抗控制端。。              |

| VDD.                    | 电源电压 (2.5V)。。             |

| VDDQ <sub>0</sub>       | 输出 IO 电源电压 (1.5V 或 1.8V)。 |

| VSS.                    | 地管脚。。                     |

| TMS, TCK, TDI, TDO      | JTAG 测试模式控制管脚。。           |

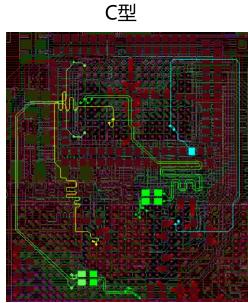

# 随机存储器-静态RAM QDR PQDR的布局 P布局与DDR类似 A型

# 随机存储器-静态RAM QDR

B型

### **▶QDR的布局**

▶布局与DDR类似

# 随机存储器-静态RAM QDR

# **▶QDR**的时序设计

| 7 | QDR信号数据信号   | QDR_0_D0-17     | 组内信号误差25mi1正负 |

|---|-------------|-----------------|---------------|

|   |             | QDR_0_Q0-17     |               |

| 8 | QDR信号时钟信号   | QDR_O_K         | 时钟差分误差小于10mil |

|   |             | QDR_O_K_N       | 不同差分对尽量等长     |

|   |             | QDR_O_C         |               |

|   |             | QDR_0_C_N       |               |

|   |             | QDR_O_CQ        |               |

|   |             | QDR_O_CQ_N      |               |

| 9 | QDR地址命令控制信号 | QDR_0_A0-18     | 尽量等长          |

|   |             | QDR_O_BWNO      |               |

|   |             | QDR_O_BWN1      |               |

|   |             | QDR_O_RN        |               |

|   |             | QDR_O_WN        |               |

|   |             | QDR_0_ZQ        |               |

|   |             | QDR_0_DLL_OFF_N |               |

# 随机存储器-静态RAM QDR

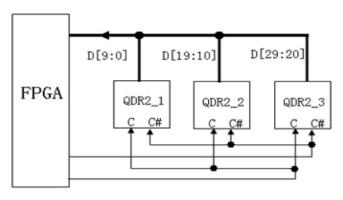

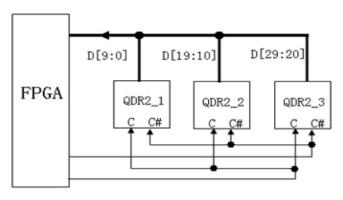

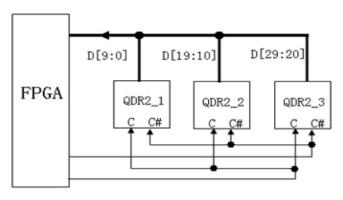

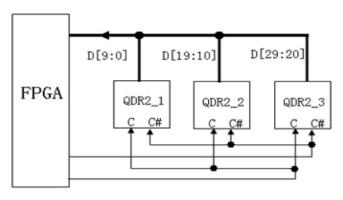

QDR2 SRAM规范中要求K/K#时钟和C/C#时钟的偏移必须大于0,因为QDR的同时读写特点,假设在同一时钟周期内,要对同一个地址的数据进行读操作和写操作,规范要求是,要先进行写操作,后进行读操作,也就是写参考时钟K/K#需要比读参考时钟C/C#先到达。但是,规范中同时规定,C/C#时钟与K/K#时钟之间的skew必须小于三分之一时钟周期。

因此如果将多片QDR2 SRAM器件并联使用的并且有C/C#时钟的话,需要注意C/C#时钟的PCB走线方式,即C/C#时钟须先到达最远端的QDR器件,最后到达最近处的QDR器件,这样,参考时钟信号的延迟正好可以抵消数据信号的延迟,确保几个器件上的数据保持同步,如下图所示。

# 随机存储器-静态RAM QDR

QDR2等长要求(推荐以Layout Guide为准、以仿真结果为准):

- 一. 输入时钟K/K#和写数据信号D[17:0]设为一个组等长,组内误差+/-25mil;

- 二. 输出时钟CQ/CQ#和读数据信号Q[17:0]设为一个组等长,组内误差+/-25mil;

- 三. 其他地址信号和控制信号设为一个组等长,组内误差+/-50mil,同时与系统时钟K/K#误差+/-100mil,与数据组误差+/-100mil;

- 四. 差分线组内误差+/-5mil;

其实由上述规则可以看出,读、写数据和地址、控制信号,以及输入输出时钟是存在时序关系的,因此,在等长设定时可将左右信号设成一个组等长,误差设为+/-25mil:

Altıum.

### DDR4

| Specification            | DDR2     | DDR3         | DDR4      |

|--------------------------|----------|--------------|-----------|

| Voltage                  | 1.8 V    | 1.5 / 1.35 V | 1.2 V     |

| Per Pin Data Rate (Mbps) | 400-1066 | 800-2133     | 1600-3200 |

3.2-8.5

512 MB-2 GB

Lower VDD voltage and Pseudo-Open Drain (POD) reduces power consumption by 40%

Channel Bandwidth (GBps)

Component Density

- Internal VREF training performed within the IC receiver, to optimize VREF level. Retraining at regular intervals.

- Data lines are calibrated at the IC, to reduce their skew to the strobe.

- Data bus inversion (DBI)

12.8-25.6

2-16 GB

DDR3 Push-Pull

6.4-17

1-8 GB

DDR4 Pseudo-Open Drain

### Altıum. DDR4 **DDR4 High Speed => Less Timing Margin** Shrinking Timing Margins in Picoseconds ■ DRAM Margin Package / Board Margin Chip Margin → Data Valid Window 2,500 Package/ Data Valid DRAM Board Window Margin Margin Margin DDR1 2,500 900 800 800 DDR2 938 425 256 256 DDR3 469 188 140 140 DDR4 125 313 938 313 DDR1 DDR2 DDR4 DDR3 3,200 Mbps 400 Mbps Image Source: Altera

# DDR4

|                          | DDRx SDRAM参数 |          |            |            |                |                                |

|--------------------------|--------------|----------|------------|------------|----------------|--------------------------------|

|                          | DDR          | DDR2     | LPDDR2     | DDR3       | LPDDR3         | DDR4                           |

| 速率(Mbps)                 | 200 ~ 400    | 400 ~800 | 333 ~ 1066 | 800 ~ 2133 | 1333 ~<br>2133 | 1600~3200 (SE)<br>~6400 (Diff) |

| VDDQ(V)                  | 2.5          | 1.8      | 1.2        | 1.5        | 1.2            | 1.2                            |

| 电平接口                     | SSTL_2       | SSTL_18  | HSUL_12    | SSTL_15    | HSUL_12        | POD12                          |

| 选通信号                     | 单端           | 可选单端/差分  | 差分         | 差分         | 差分             | 差分                             |

| ODT                      | 无            | 有        | 无          | 有          | 可选             | 有                              |

| Slew<br>RateDerati<br>ng | 有            | 有        | 有          | 有          | 有              | 无                              |

| WriteLeveli<br>ng        | 无            | 无        | 无          | 有          | 有              | 有                              |

| DBI                      | 无            | 无        | 无          | 无          | 无              | 有                              |

# DDR4

### DDR3 新功能

- DDR3新增的重置(Reset)功能

- □ DDR3新增ZO校准功能

- □ 突发长度(Burst Length, BL),由于DDR3的预取为8bit,所以突发传输周期(Burst Length, BL)也固定为8

- □ 寻址时序(Timing)变化

- ① 参考电压分成两个VREF将分为两个信号,即为命令与地址信号服务的VREFCA和为数据总线服务的REFDQ,这将有效地提高系统数据总线的信噪等级

### DDR4

### DDR4 新功能

- □ 新的JEDEC POD12接口标准(工作电压1.2V);

- □ DBI: 可以降低功耗并且提升数据信号完整性;

- □ Bank群组结构: 是个8n预取群组结构,它可以使用两个或者四个Bank组,这允许DDR4内存在每个Bank群组单独被激活、读取、写入或刷新操作,这样可以带来更高的内存速度和带宽;

- □ 取消了Derating,时序仿真计算不再繁琐;

- □ DQ动态确定Vref(V\_center),增加了眼图要求;

- □ 新的终止调度:在DDR4中DQ bus可以转移终止到VDDQ,这样即使VDD电压降低的情况下也能保证稳定:

- □ 新的数据总线CRC技术,可以进行传输过程中的错误侦测,特别对非ECC内存进行写入操作时有帮助;

- □ 针对命令和地址总线的新的CA奇偶校验:

- □ 突发长度和突发停止长度分别为8和4;

- □ 正常和动态的ODT:改进ODT协议,并且采用新的Park Mode模式可以允许正常终结和动态吸入终结,而不需要去驱动ODT Pin;

- □ \*Differential Signaling(差分信号技术)

# **DDR4 vs DDR3**

| 特点         | DDR3                              | DDR4                               | 备注                |  |  |  |

|------------|-----------------------------------|------------------------------------|-------------------|--|--|--|

|            | 信令变化                              |                                    |                   |  |  |  |

| 电压(内核和I/0) | 1.5V                              | 1.2V                               | 降低能耗              |  |  |  |

| 低压标准       | 是(DDR3L@ 1.35V)                   | 预计(DDR4L,可能1.05V)                  | 内存能耗下降            |  |  |  |

| 数据速率(MT/s) | 800, 1066, 1333, 1600, 1866, 2133 | 1600, 1867, 2133, 2400, 2667, 3200 | 演进到更高速度           |  |  |  |

| 密度         | 512Mb - 8Gb                       | 2Gb -16Gb                          | 满足更高容量的内存<br>需求   |  |  |  |

| DBI        | 无                                 | 有                                  | 更低功耗和更好的信<br>号完整性 |  |  |  |

| DQ驱动器(ALT) | 40欧姆                              | 48欧姆                               | 为点到点应用优化          |  |  |  |

| DQ总线       | SSTL 15                           | POD 12                             | 降低I/0噪声和能耗        |  |  |  |

| RTT值       | 120, 60, 40, 30, 20               | 240, 120, 80, 60, 48, 40, 34       | 支持更高的数据速          |  |  |  |

| 堆叠引脚       | 否                                 | 是                                  | 适用于未来的更高密<br>度的模块 |  |  |  |

# DDR4 Skew/等长

|                                                                                                        | DDR3                                                     | DDR4                                            |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------|

|                                                                                                        | 同组DQ/ECC与对应DQS等长保持在100mi1内                               | 同组DQ/ECC与对应DQS等长保持在50mi1内                       |

| Source-Synchronous Signal                                                                              | DQS 差分线对内等长保持在5mi1内                                      | DQS 差分线对内等长保持在5mi1内                             |

| Source-Synchronous Signar                                                                              | 司组DQ/ECC等长保持在30mi1内                                      | 同组DO/ECC等长保持在10mi1内                             |

|                                                                                                        | 同组信号严格要求同层走线                                             | 同组信号严格要求同层走线                                    |

| Clock Signal                                                                                           | CLK差分线对内等长保持在2mi1内                                       | CLK差分线对内等长保持在2mi1内                              |

| Clock Signal                                                                                           | 同一DIMM的CLK之间等长保持在20mi1内                                  | 司一DIMM的CLK之间等长保持在5mi1内                          |

| Source Clocked<br>Signal (MA[15:00], BA[2:0], RA<br>S_N, CAS_N, WE_N, MA_PAR)/BG<br>[1:0], ACT_N, C[2] | 同一个DLL组.CMD要求等长保持在500mil内所有CMD信号要求与对应时钟保持在2inch内         | 同一个DLL组,CMD要求等长保持在25mi1内所有CMD信号要求与对应时钟保持在2inch内 |

| Source Clocked<br>SignalCS_N[9:0], ODT[5:0], CK<br>E[5:0]                                              | 同一个DLL组, UDIMM CTL要求与时钟等长保持在100mil内, for RDIMM保持在240mil内 | 同一个DLL组,CTL要求与时钟等长保持在25mi1内,for RDIMM保持在100mi1内 |

DDR3摘自Intel Romley PDG; DDR4摘自Intel Grantley PDG

# DDR4 Crosstalk/串扰

|                                                                                                | DDR3                                                                                      | DDR4                                                                                                       |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

|                                                                                                | 同组DO/ECC/DOS最小间距:内层17mil(4.25H)外层19mil(7.03H)                                             | 同组DO/ECC/DOS最小间距:内层17mil(4.25H)外层19mil(7.03H)                                                              |

| Source-Synchronous Signal                                                                      | 组间DQ/ECC最小间距: 内层32mil,外层27mil                                                             | 组间DQ/ECC最小间距:内层32mil,外层27mil                                                                               |

| 30urce-synchronous signal                                                                      | 同层通道间DQ/ECC最小间距:内层40mil,外层32mil                                                           | 同层通道间DQ/ECC最小间距:内层40mil,外层32mil                                                                            |

|                                                                                                | DQ/ECC在DIMM Pin处间距: 内层9mil,外层12mil                                                        | DQ/ECC在DIMM Pin处间距:内层17mil,外层<br>19mil                                                                     |

| Clock Signal                                                                                   | CLK差分线对内间距5mil                                                                            | CLK差分线对内间距5mil                                                                                             |

| Clock Signal                                                                                   | CLK差分线与其他信号间距:内层12mil,外层13.5mil                                                           | CLK差分线与其他信号间距:内层12mil,外层<br>13.5mil                                                                        |

| Source Clocked<br>Signal(MA[15:00],BA[2:0],RA<br>S_N,CAS_N,WE_N,MA_PAR)/<br>BG[1:0],ÄCT_N,C[2] | CMD信号之间间距:内层12mil,外层13.5milCMD信号与DQ信号最小间距:内层32mil,外层27milCMD信号在DIMM Pin处间距:内层9mil,外层12mil | CMD信号之间间距:内层12mil,外层13.5milCMD<br>信号与DQ信号最小间距: 内层32mil,外层<br>27milCMD信号在DIMM Pin处间距: 内层4.9mil,<br>外层6.9mil |

| Source Clocked<br>signalCS_N[9:0],ODT[5:0],CK<br>E[5:0]                                        | CTL信号之间间距内层12mil,外层13.5milCTL信号与DQ信号最小间距:内层32mil,外层27milCTL信号在DIMM Pin处间距:内层9mil,外层12mil  | CTL信号之间间距: 内层12mil,外层13.5milCTL信号与DC信号最小间距: 内层32mil,外层27milCTL信号在DIMM Pin处间距: 内层4.9mil,外层6.9mil            |

DDR3摘自Intel Romley PDG; DDR4摘自Intel Grantley PDG

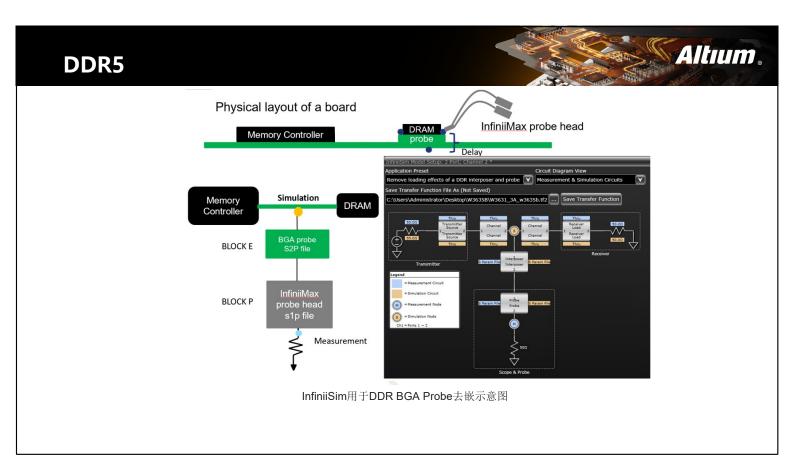

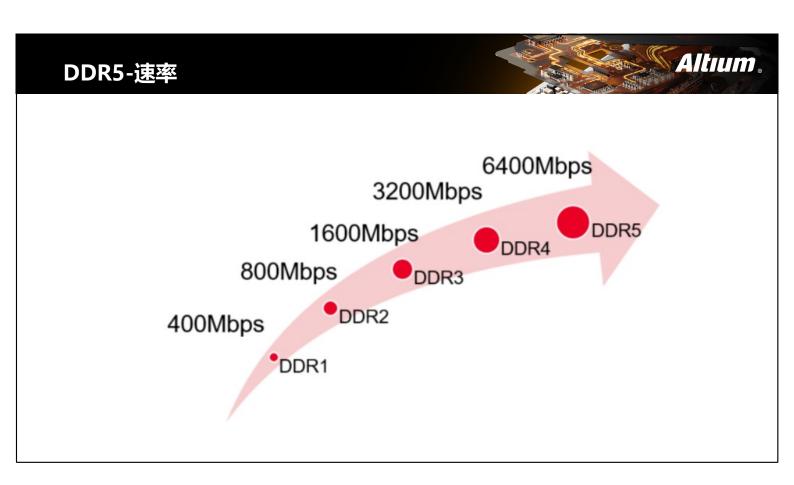

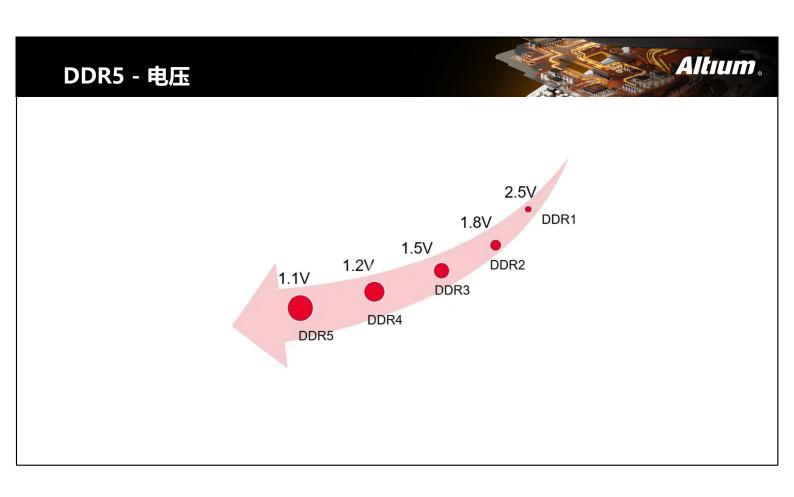

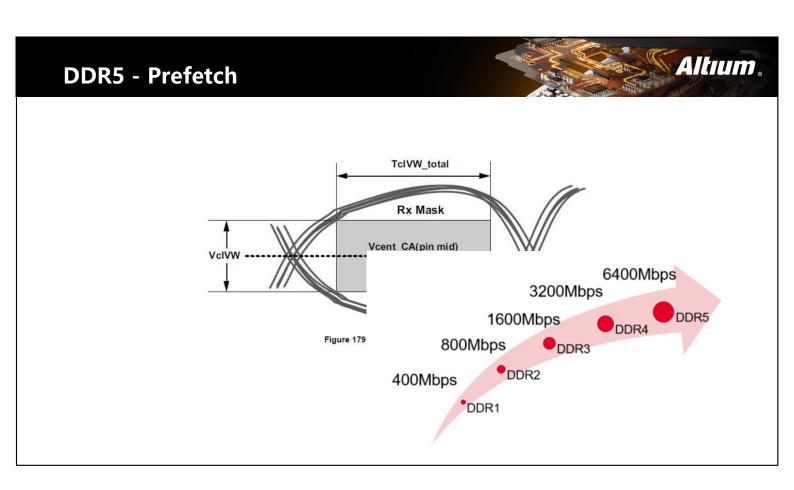

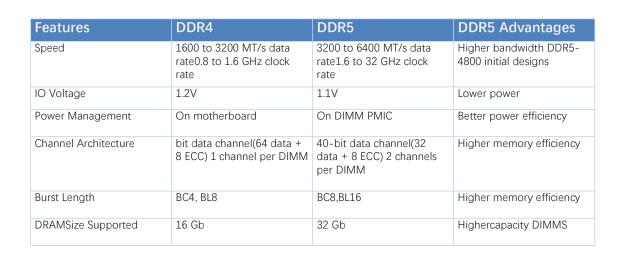

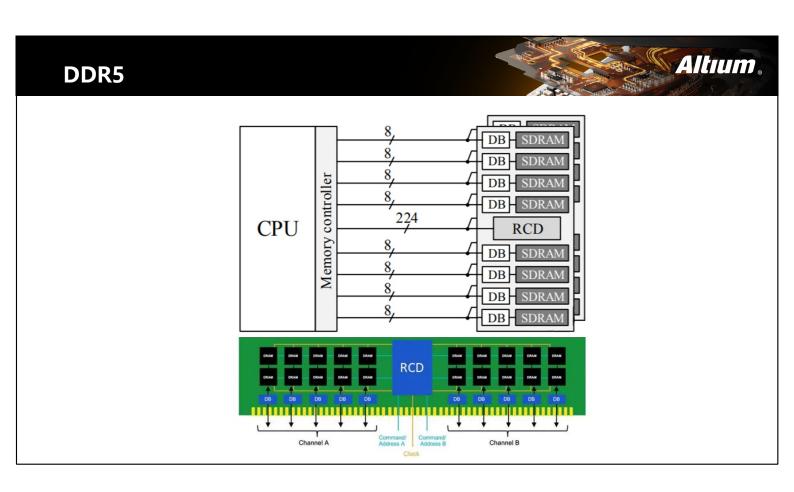

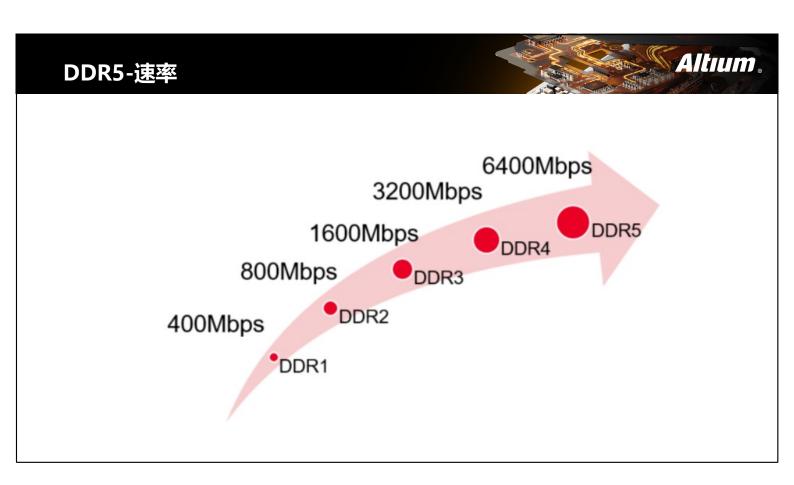

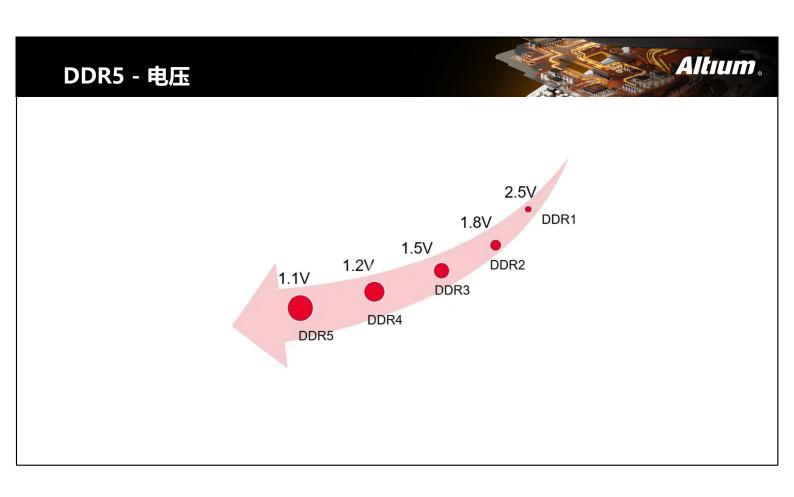

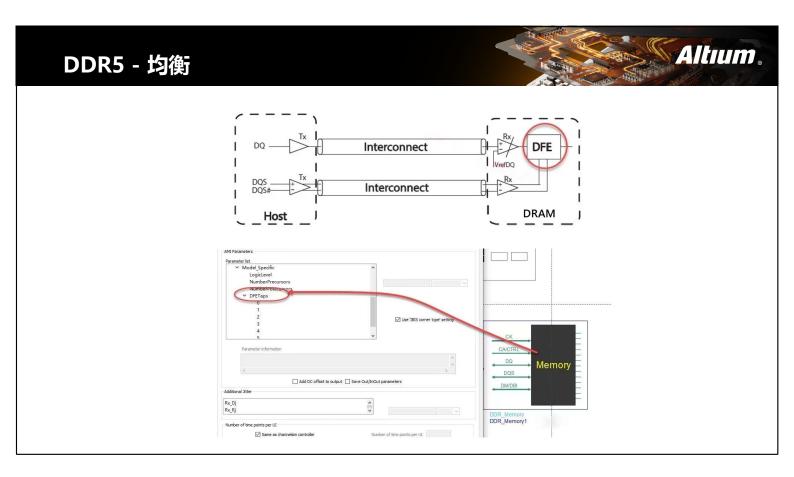

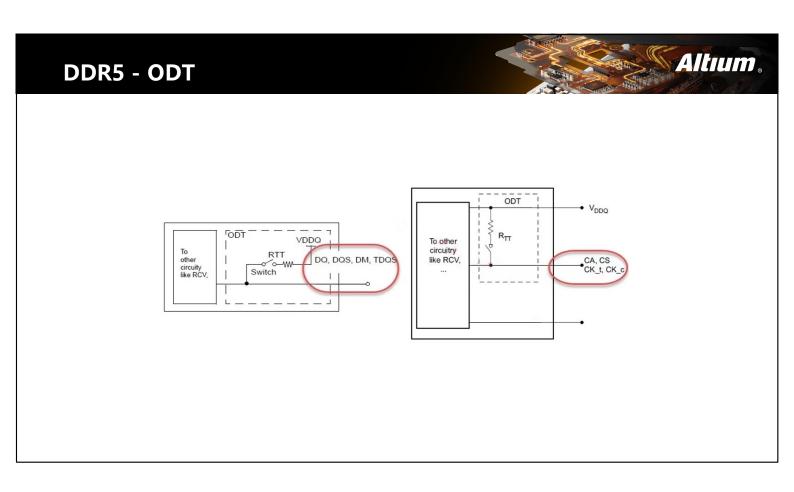

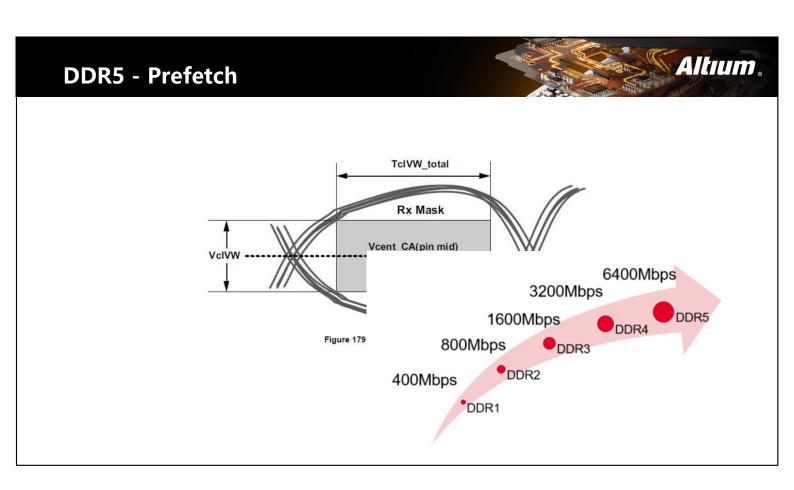

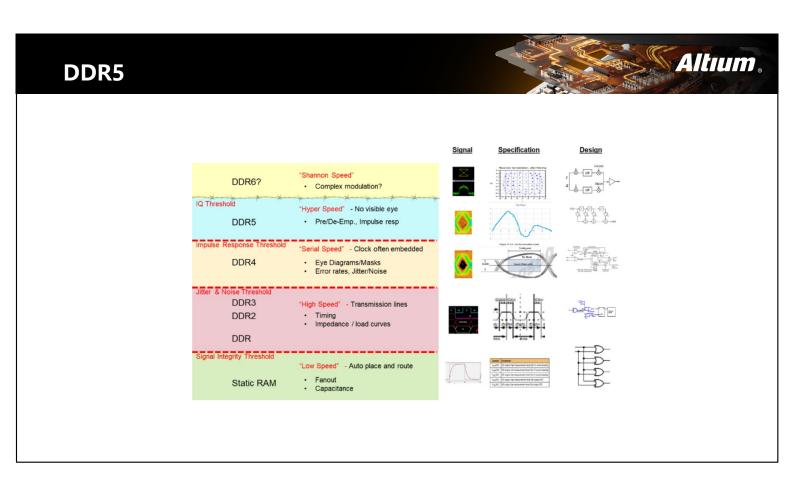

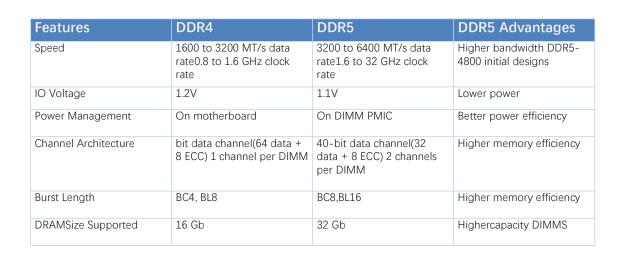

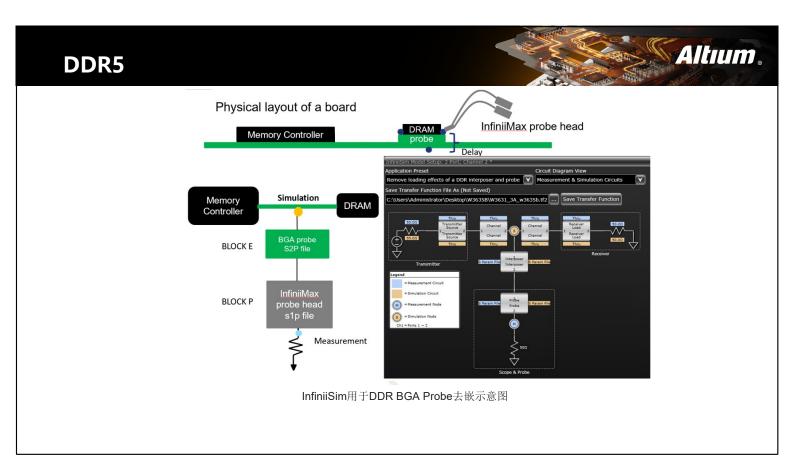

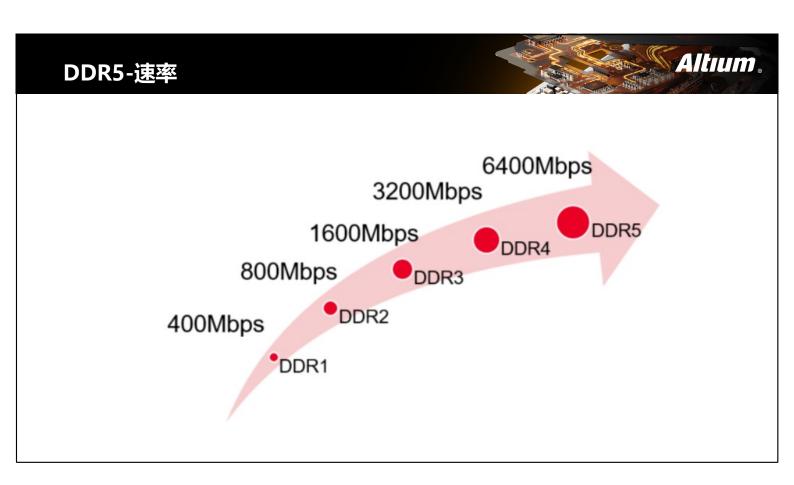

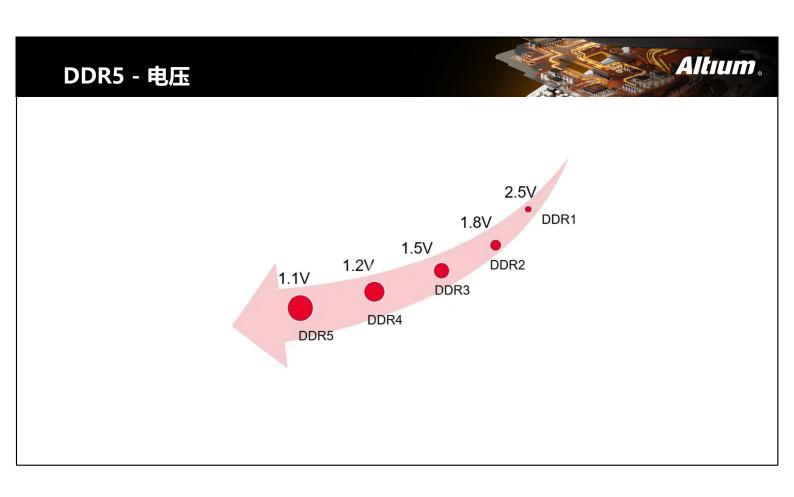

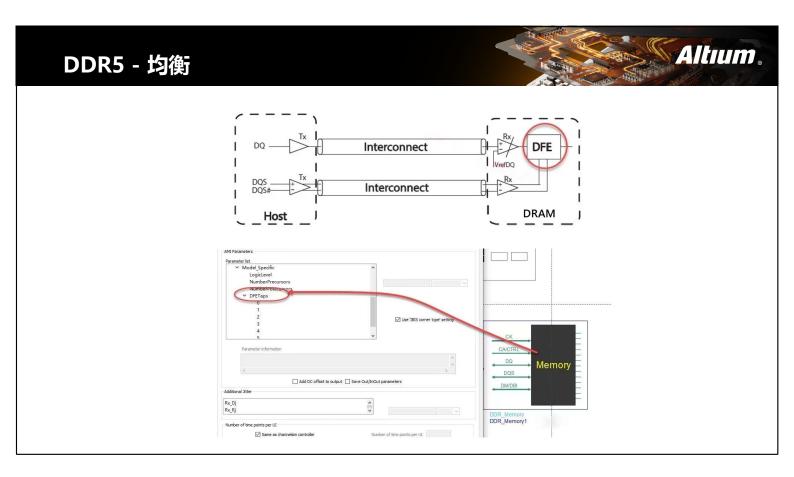

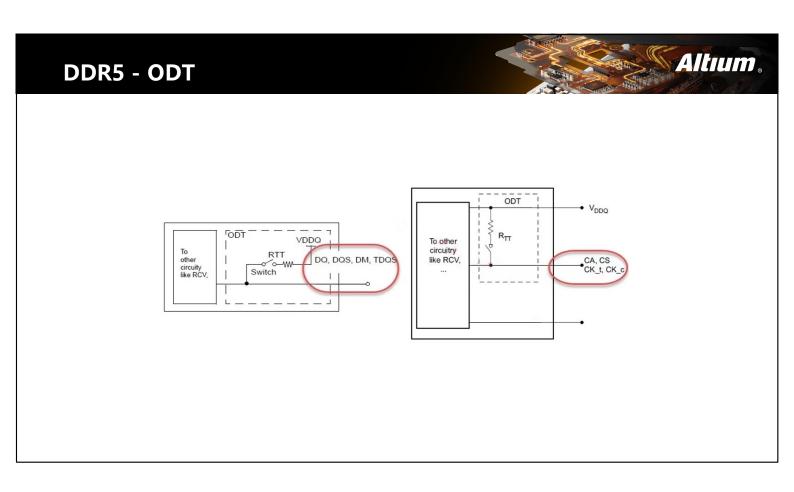

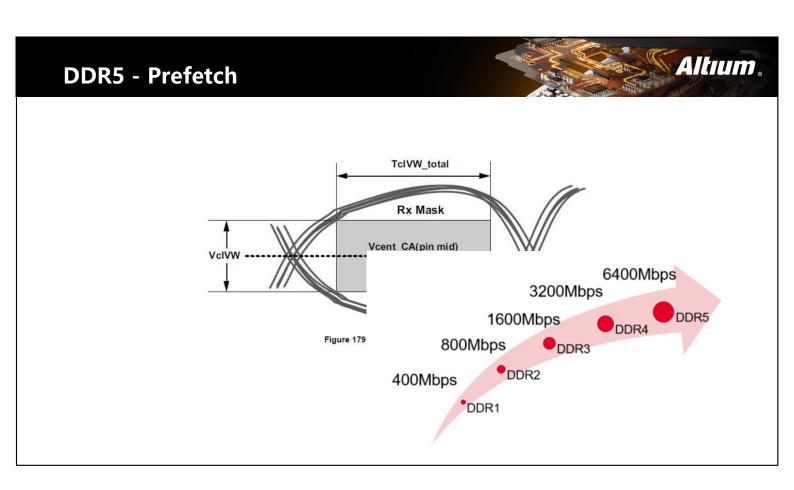

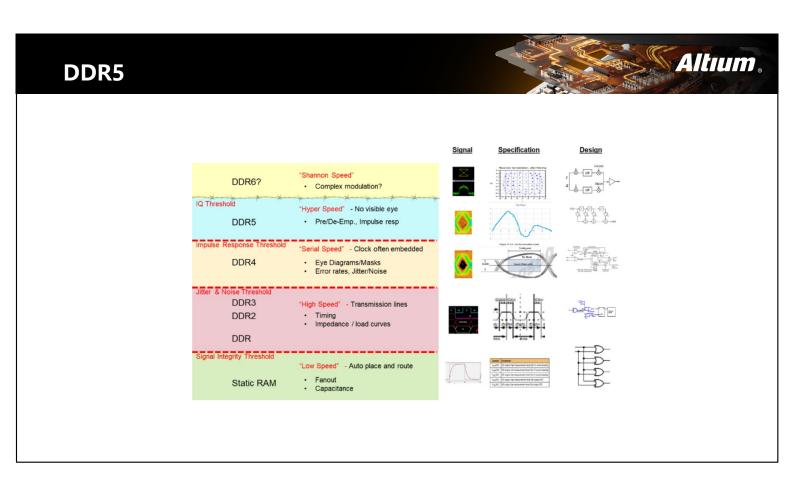

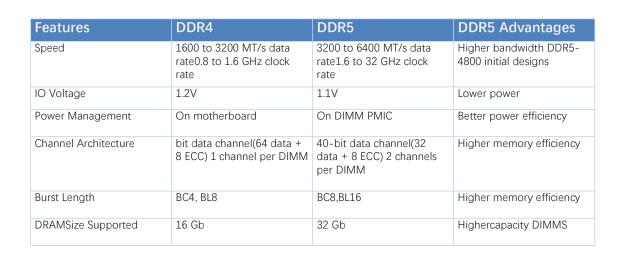

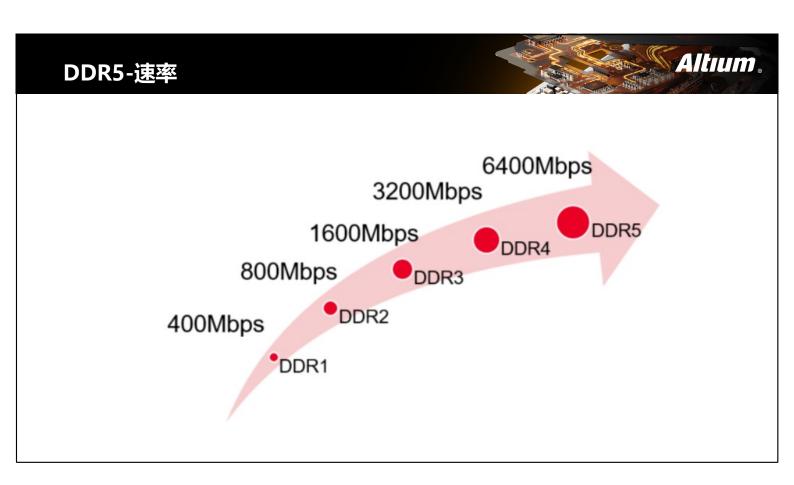

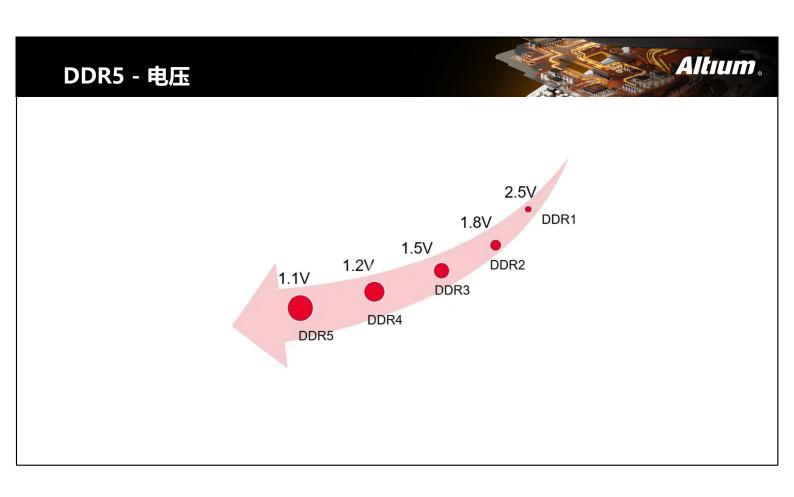

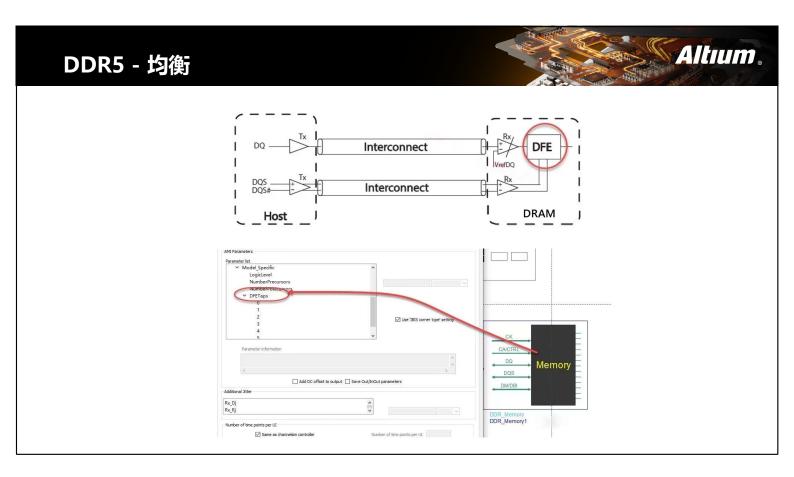

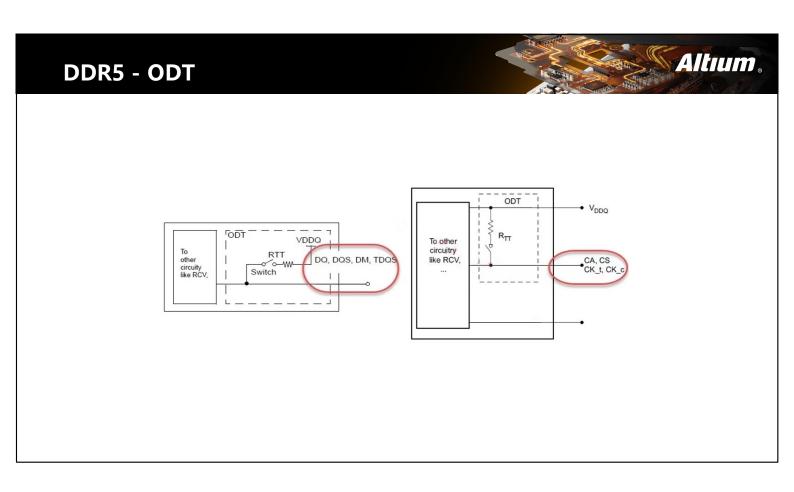

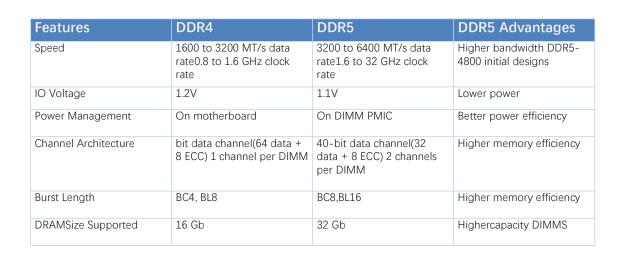

# DDR5 vs DDR4

| 对比项目     | DDR4      | DDR5      |

|----------|-----------|-----------|

| 速率       | 1.6G~3.2G | 3.2G~6.4G |

| 电压       | 1.2V      | 1.1V      |

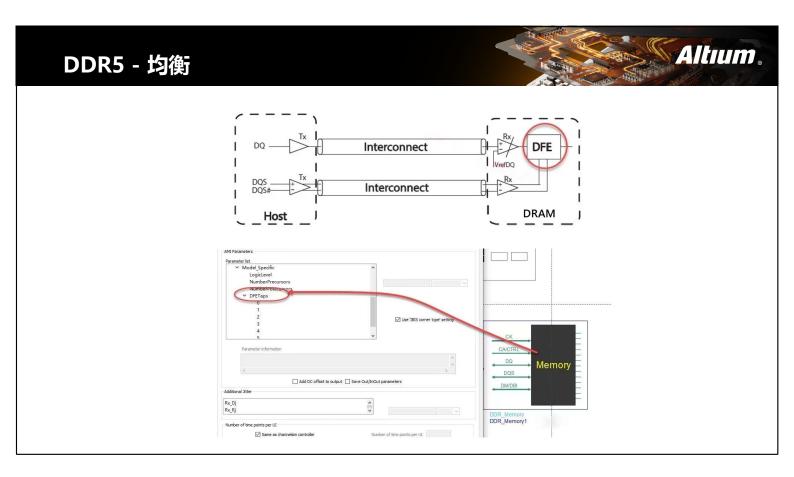

| 均衡       | 无         | 有         |

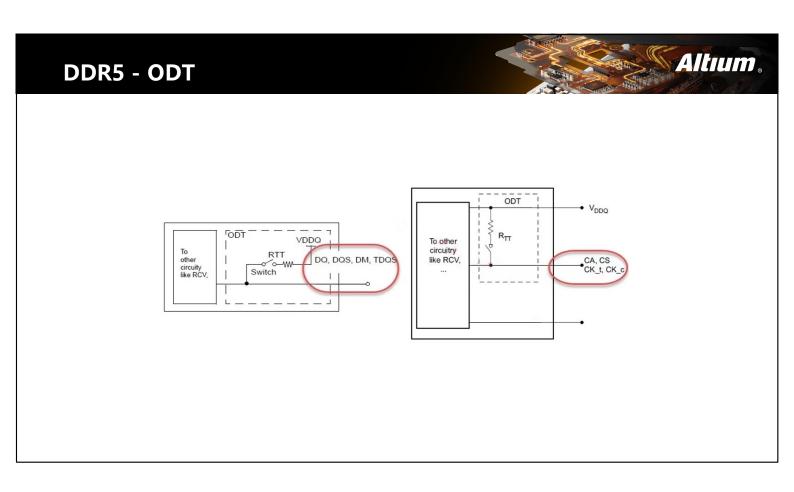

| ODT      | DQ        | DQ,CA     |

| Prefetch | 8n        | 16n       |

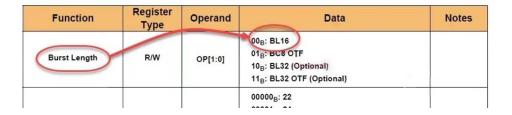

| BL       | BL8       | BL16      |

| 单颗DRAM容量 | 16Gb      | 32Gb      |

Altıum.

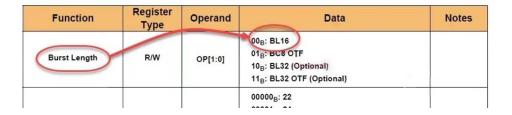

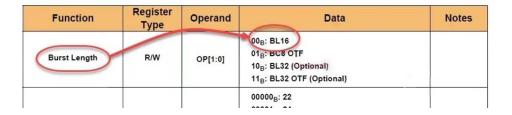

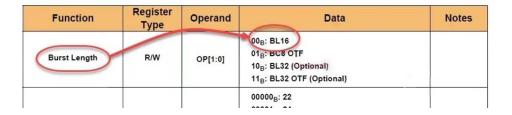

## **DDR5** - Burst length

Altium.

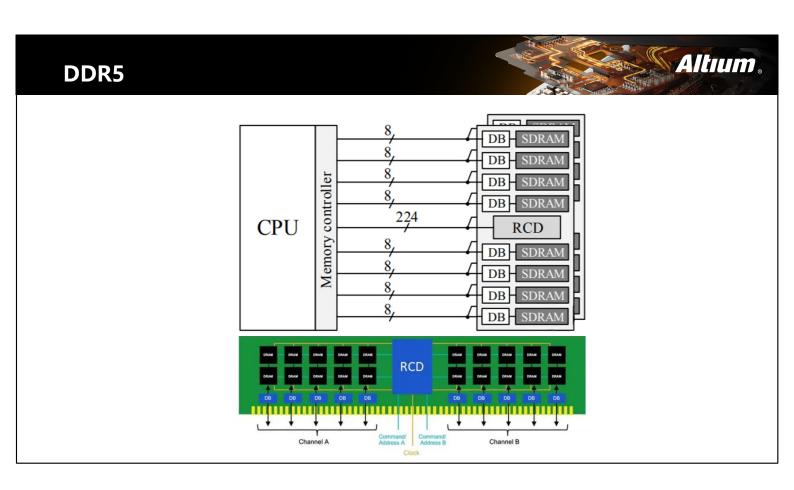

## DDR5

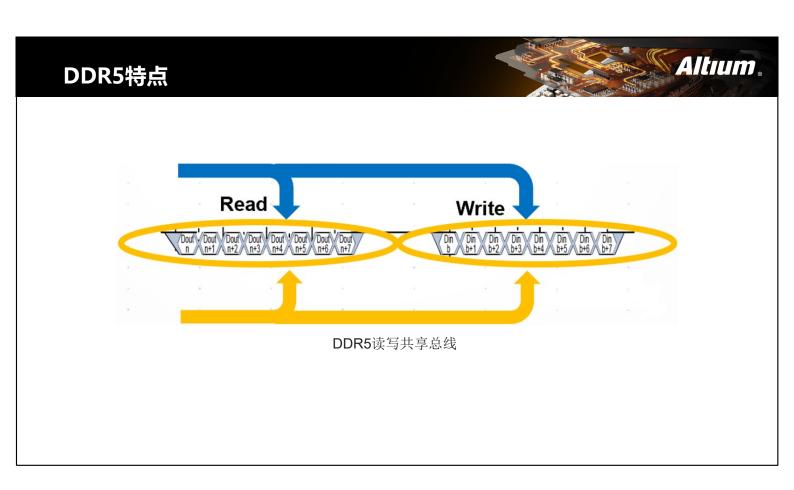

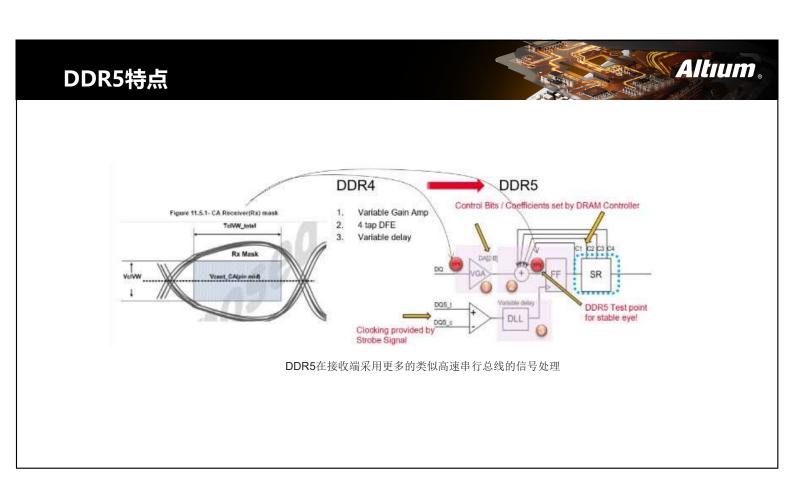

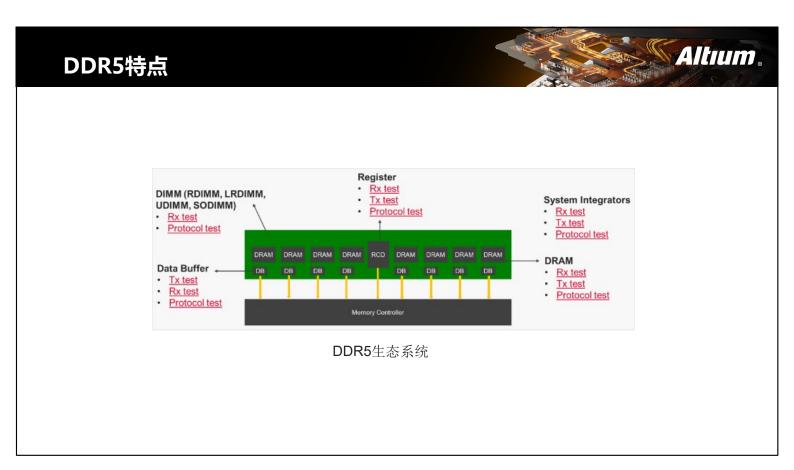

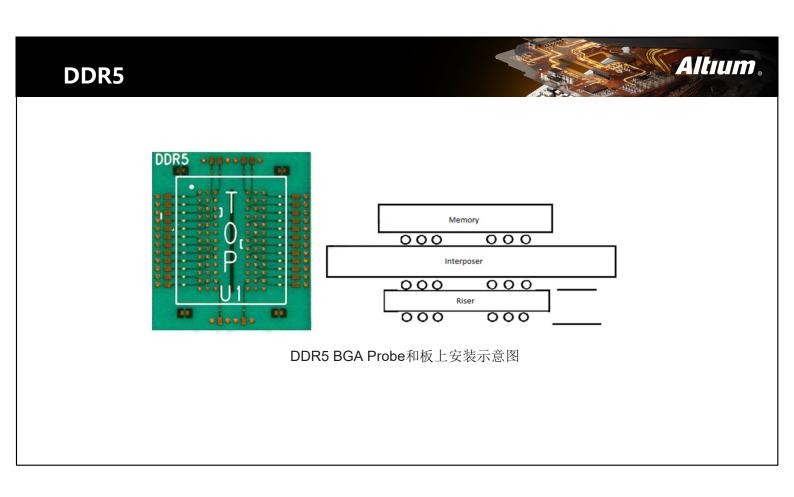

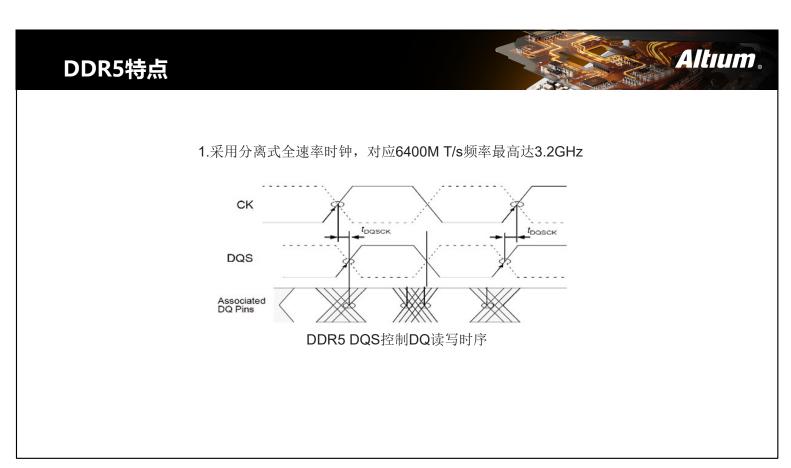

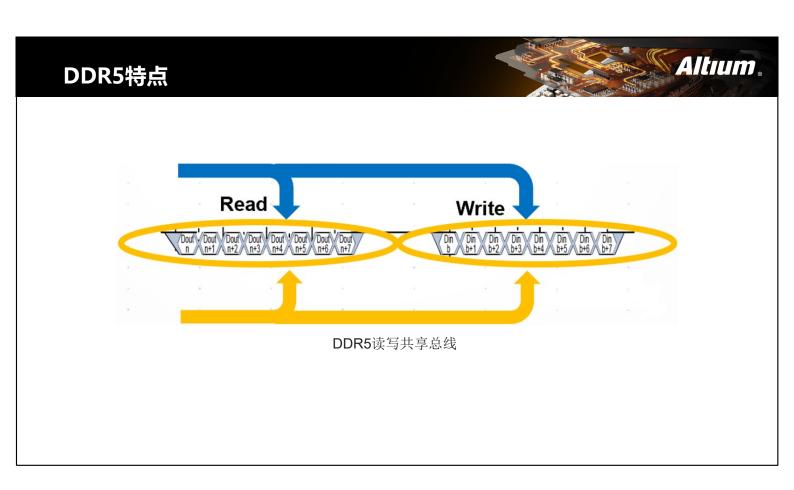

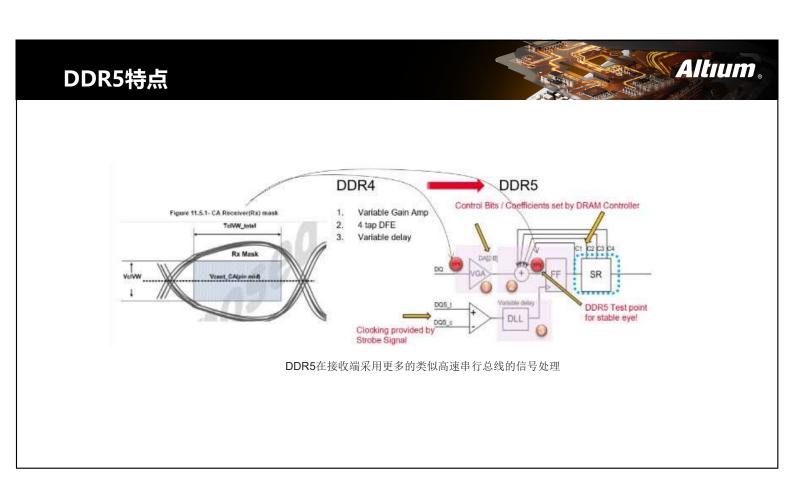

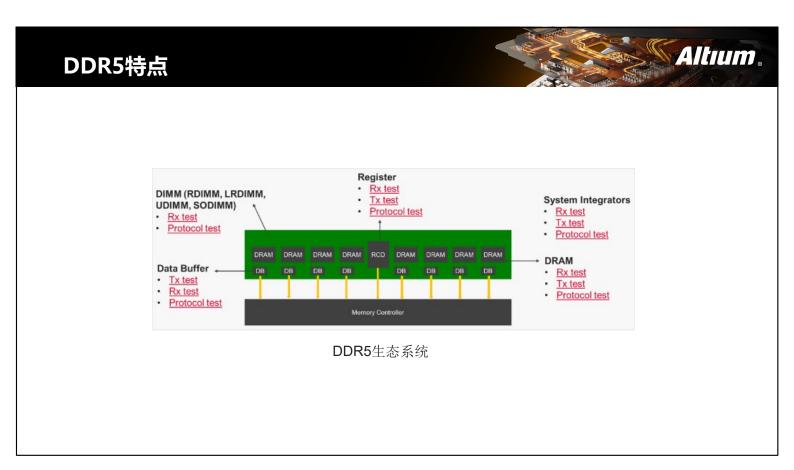

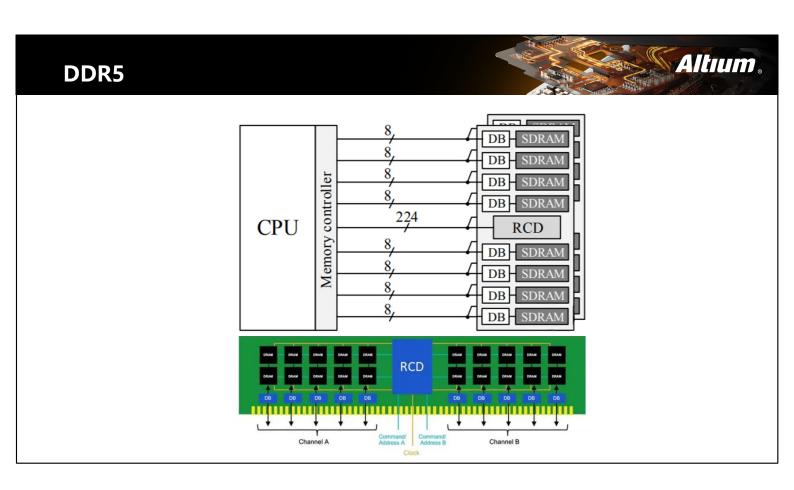

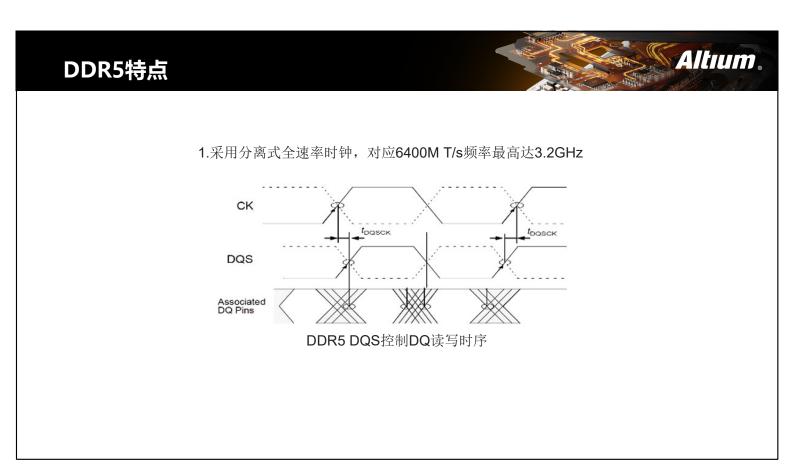

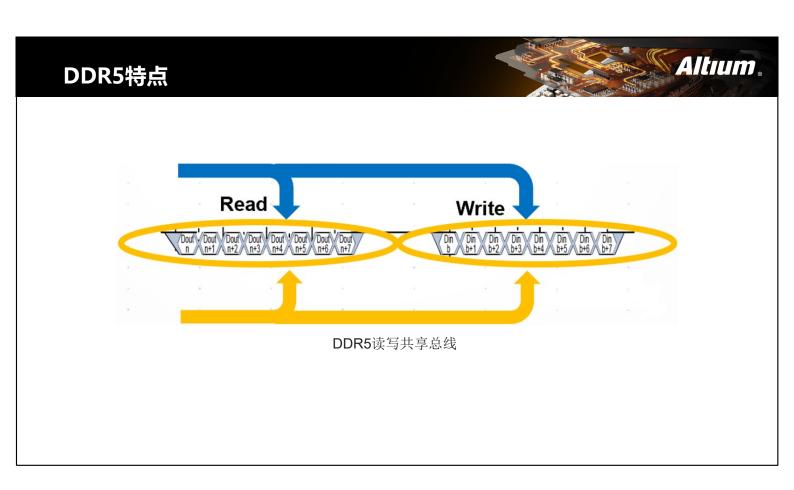

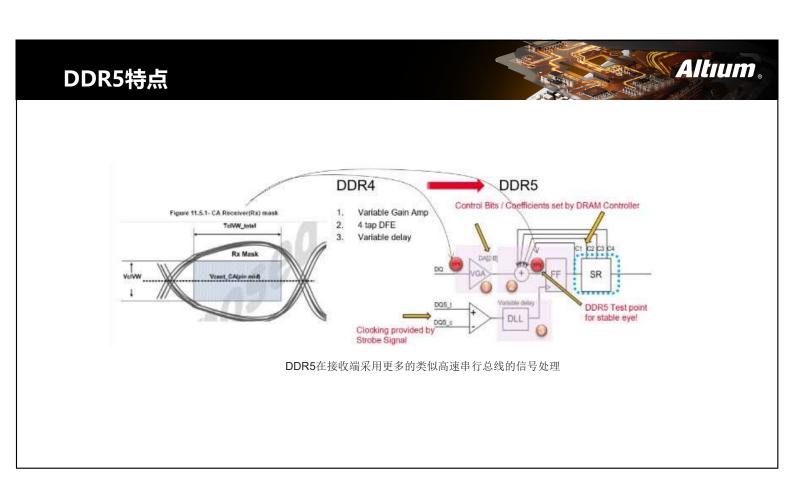

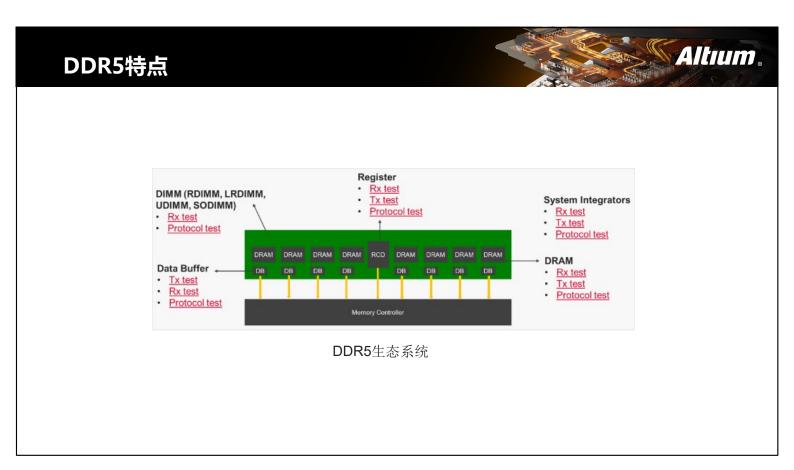

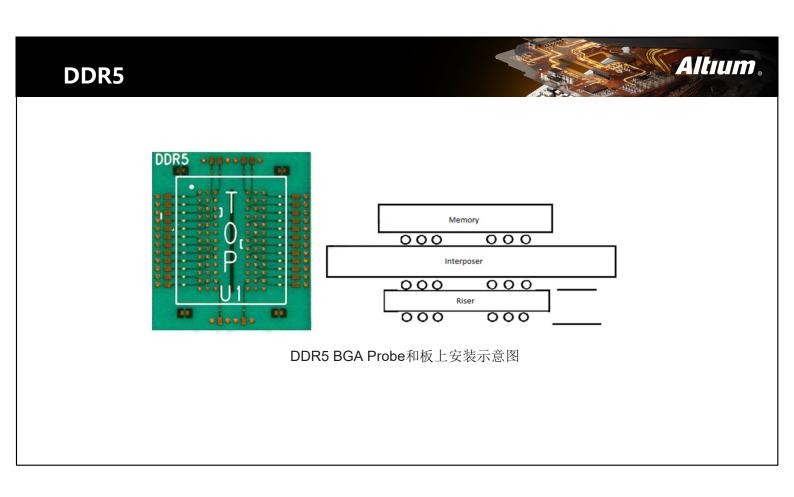

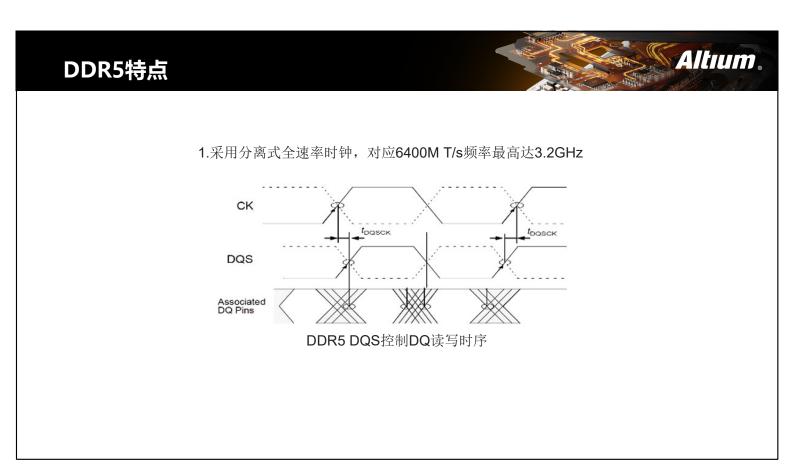

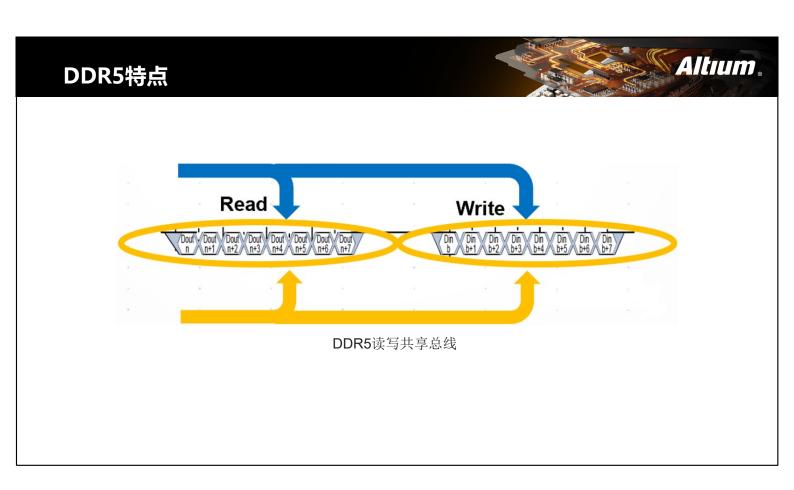

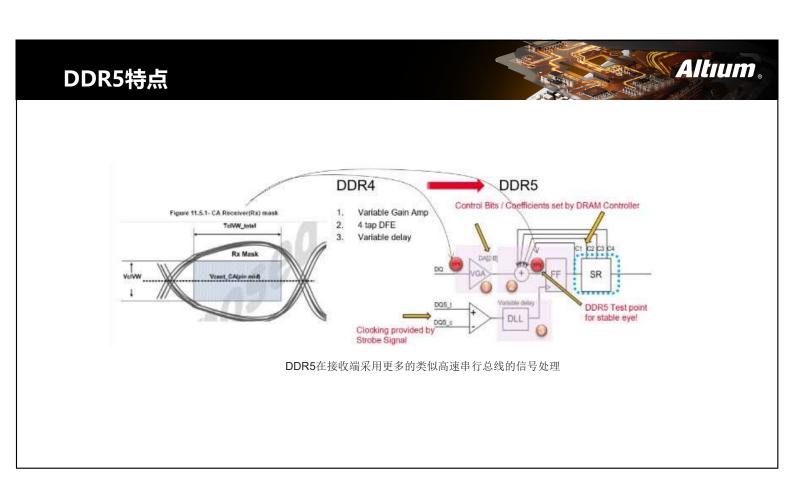

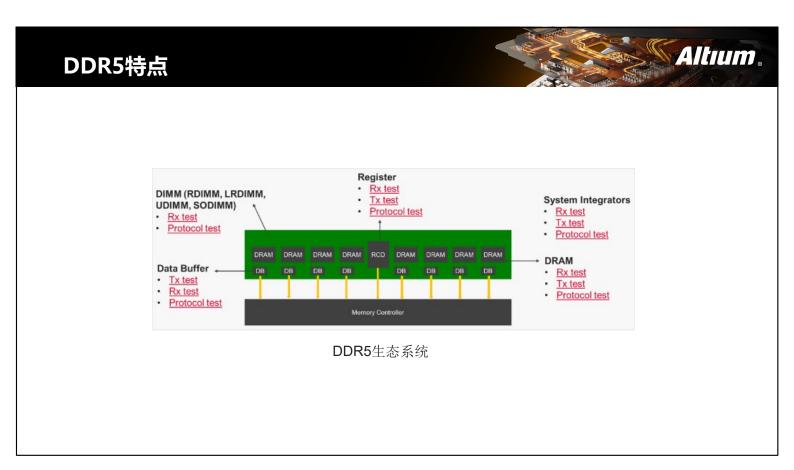

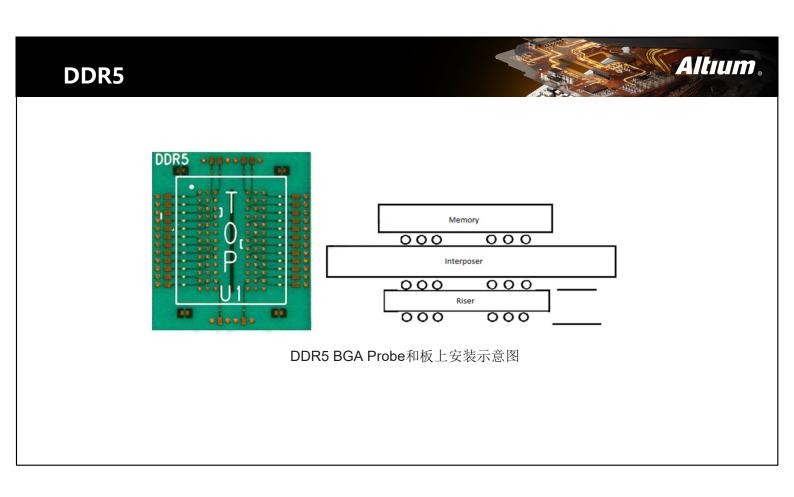

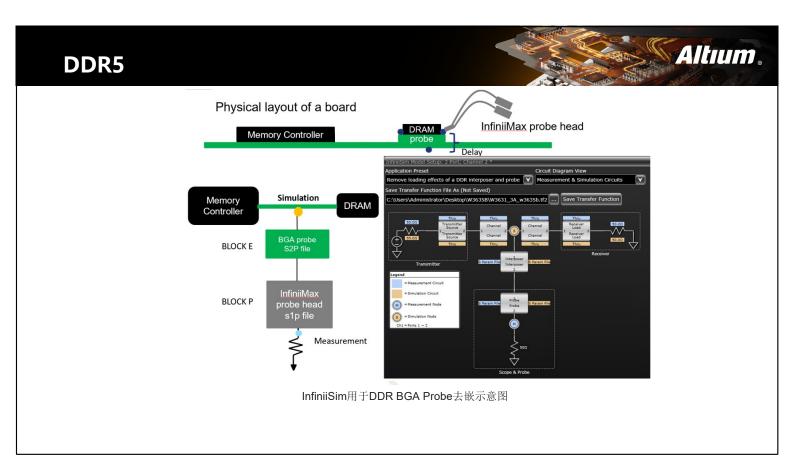

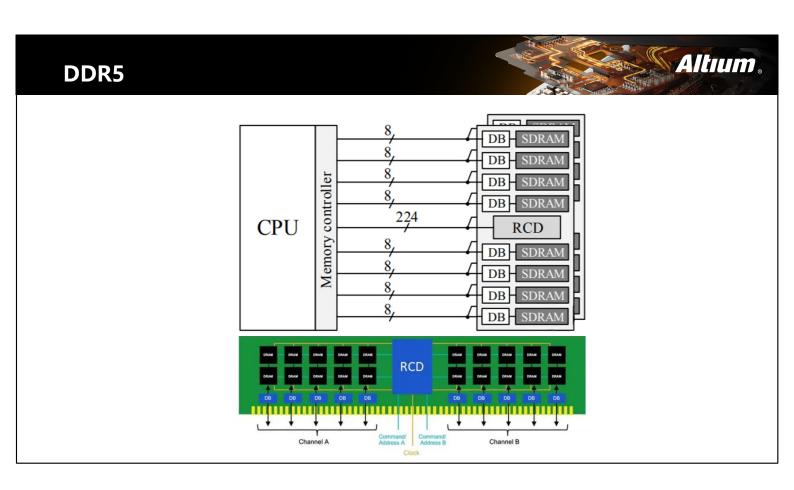

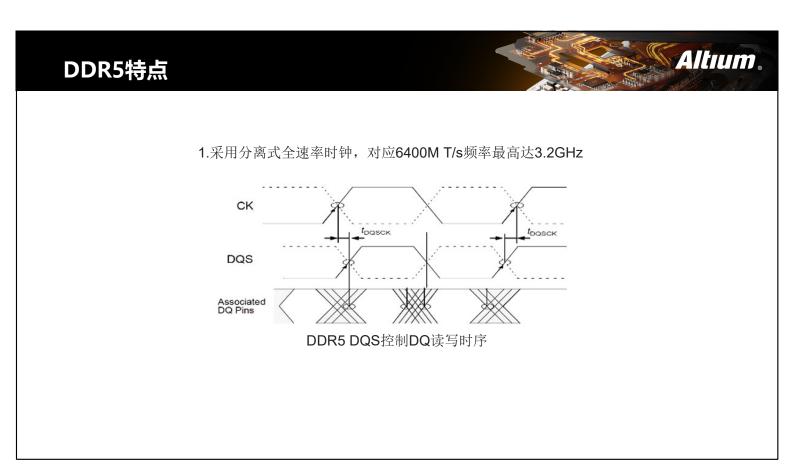

## DDR5特点

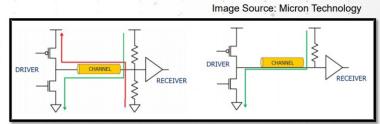

2.更宽的总线,单端信号,从RCD(Registering ClockDrivers)芯片来看采用Multi-Drop架构。

基于今天更宽的总线需求,在一块刀片服务器上可能支持1000+个并行数据通道。且由于继续采用单端信号且速率倍增,传统只在串行差分电路上考虑的损耗问题也开始困扰DDR5.因此在DDR5设计和验证测试上,不仅需要考虑传统的串扰问题还增加了对电路损耗问题的考虑

Altıum.

## 只读存储器ROM-FLASH

Altıum.

- ➤ FLASH特点

- ▶ 速率较低,通常在50Mhz以下

- ▶ 静态存储

- > 布局

- > 一般采用菊花链

- > Flash和SDRAM的推荐距离为500-1000mil

## 只读存储器ROM-FLASH

- > 特性阻抗:50欧

- > 线间距3W

- > 等长范围:+/-100mil

#### 只读存储器ROM-EEPROM电路概述

#### **EEPROM**

EEPROM(电可擦可编程只读存储器)这是一种具有可擦除功能,擦除后即可进行再编程的ROM内存,一种掉电后数据不丢失的存储芯片,EEPROM可以在电脑上或专用设备上擦除已有信息,重新编程。这类芯片一般用于即插即用。

## 只读存储器ROM-EEPROM典型电路

Vcc

- 1.在某些器件中,引脚A0,A1,A2在内部未连接

- 2.应使用一个去耦合电容(通常为0.1UF)来帮助滤除VCC上的小纹波

## 只读存储器ROM-EEPROM典型电路

1.2.3: A0 A1 A2 器件地址选择

5: SDA 串行数据,地址

▶ 管脚定义 6: SCL 串行时钟

7: WP 写保护

8: VCC +1.8V~6.0V工作电压

## 只读存储器ROM-EEPROM布局要求

> 靠近主芯片放置,使距离尽量短

## 只读存储器ROM-EEPROM布线要求

#### **EEPROM**电路布线要求

- (1) 控制50欧姆阻抗。

- (2) 两根线并行走,与其他信号线保持3W以上的间距。

- (3) 尽量在表层走线;如需换层,需要有完整的参考平面,保持阻抗 连续性;并保证过孔数量不超过3个。

且在换层处100mil以内添加一个或者两个回流地孔。

## 随机存储器-动态RAM SDRAM

#### > SDRAM (同步动态随机存储器)

#### > 管脚定义解释

| 信号名。             | 功能描述。    |

|------------------|----------|

| CLK.             | 时钟。      |

| CKE.             | 时钟使能。    |

| CS#.             | 片选。      |

| WE#.             | 读写。      |

| RAS#.            | 列选。      |

| CAS#.            | 行选。      |

| DQM <sub>e</sub> | 数据掩码。    |

| BAO, BA1.        | Bank 选择。 |

| A 0-A 1 1.       | 地址。      |

| DQ 0-DQ 15.      | 数据(输出)。  |

| VDDQ.            | DQ 电源。   |

| VSSQ.            | DQ 地。    |

| VDD.             | 电源。      |

| VSS.             | 地。       |

## 随机存储器-动态RAM SDRAM

- ➤ SDRAM的布局原则: 靠近CPU放置

- > SDRAM X 1片时:点对点的布局方式

- > SDRAM到CPU的中心距离为:

当中间无排阻时: 900-1000mil 当中间有排阻时: 1000-1300mil

### 随机存储器-动态RAM SDRAM

#### ➤ SDRAM的布局原则:

➤ SDRAM X 2片时:相对于CPU严格对称

方案一: 顶底对贴(推荐)

方案二:与CPU放在同一面

## 随机存储器-动态RAM SDRAM

# Altium.

#### > SDRAM的布线

- > 特性阻抗:50欧姆

- ▶ 数据线每9根尽量走在同一层(D0~D7,LDQM;D8~D15,HDQM)

- > 数据线、地址(控制)线、时钟线之间的距离保持20mil以上或至少3W

- ➢ 空间允许的情况下,应该在它们走线之间加一根地线进行隔离。地线宽度推荐为15-30mil

- > 完整的参考平面

- ➤ 布线拓扑结构(默认采用远端分支)-T点(过孔)打在两片SDRAM中间

## Altium. 随机存储器-动态RAM SDRAM > SDRAM的拓扑结构 远端分支(星形/T形) 菊花链 - 地址控制线 • 地址控制线 - 数据线时钟线 数据线时钟线

## 随机存储器-动态RAM SDRAM

- >SDRAM的等长布线

- > Class规则:

将所有数据线设为sdram\_data\_bus; 地址线,控制线,时钟线设为sdram\_addr\_bus

> 等长规则:

所有信号线参照时钟线的长度等长

> 误差范围:

数据线误差范围控制在+/- 50mil 地址线误差范围控制在+/- 100mil

Altıum.

## 随机存储器-动态RAM DDR

#### >DDR的设计

管脚定义解释

| 管脚数₽            | 信号名。            | 功能描述。            | ¢3  |

|-----------------|-----------------|------------------|-----|

| 20              | CK, CK#         | 全局时钟输入。₽         | ÷   |

| 10              | CKE.            | 时钟使能信号输入。。       | t)  |

| 10              | CS#ø            | 片选信号输入。₽         | 4J  |

| 3₽              | RAS#, CAS#, WE# | 命令信号输入。₽         | 47  |

| 20              | LDM, UDM∘       | 数据 mask 信号输入。₽   | 42  |

| 13*₽            | A<012>+         | 地址信号输入。。         | 47. |

| 2₽              | BA0, BA1        | BANK 选择信号输入。。    | 42  |

| 16*₽            | DQ<015>₽        | 数据信号输入/输出。₽      | φ   |

| 2₽              | LDQS, UDQS      | 数据锁存信号输入/输出。₽    | 47  |

| 5* <sub>0</sub> | NC.             | 空引脚。。            | 47  |

| 2₽              | DNU₽            | 不使用引脚。 🗸         | 47  |

| 5₽              | VDDQ₽           | DQ 电源电压 (2.5V)。₽ | 47  |

| 5₽              | VSSQ₽           | DQ 地。→           | 47  |

| 3≠              | VDDø            | 器件电源电压(2.5V)。₽   | 47  |

| 3≠              | VSS.            | 器件地。。            | 47  |

| 1₽              | VREF₽           | SSTL_2 参考电压。↩    | 47  |

DDR SDRAM 封装结构图+

DDR SDRAM 管脚功能说明。

### 随机存储器-动态RAM DDR

- ❖ 工作原理:

- 一. DDR的读写操作时序如图 所示。图中,命令信号与 地址信号参考CK信号上升 沿输入到DDR。

- 二. 读数据时DQ随着DQS并参考DQS信号沿输出,写数据时DQ随着DQS并参考DQS的信号沿输入,读写数据时DQS都是双沿有效。

- 三. 读数据时,输出的DQS由 送入DDR的差分时钟 CK/CK#使用DDR存储器 中的一个DLL生成DQS, 并使之与输出数据对齐。

- 四. 虽然DDR存储器不用差分 输入时钟来发送或接收数 据,但是所用DQS信号与 输入时钟的频率有关。

Altıum.

## 随机存储器-动态RAM DDR

#### ➤ DDR的布局

- ▶ 布局原则是: 靠近CPU摆放

- ▶ DDRx1片时,点对点的布局方式

- ▶ DDR到CPU推荐的中心距离:

当中间无排阻时: 900-1000mil

当中间有排阻时: 1000-1300mil

## Altıum. 随机存储器-动态RAM DDR **▶DDR的布局** ▶DDRx2片时,相对于CPU严格对称 X < 1660milVREF旁路电容 Y < 1280mil Y1 = Y2 < 650mi1**▶VREF电容的位置** A1方向 CPU A1方向 DDR

#### >DDR保护区域

DDR2 保护区域 (Keepout Region): DDR2 内存组,所有同 DDR 相关的阻容电路,一直向 CPU 方向延伸至 CPU 的 DDR 控制器,称为 DDR 保护区域(DDR Keepout Region)。这个区域里需满足以下条件:

- a) 不得出现与 DDR 无关的信号。

- b) 必须提供完整的地平面(信号线下方地平面不得中断)。

- c) 必须提供完整的 VCC\_1V8 电源平面 (信号线下方电源平面不得中断)。

### 随机存储器-动态RAM DDR

- > 特性阻抗:单端50欧,差分100欧

- 数据线每10根尽量走在同一层 (D0~D7,LDM,LDQS)(D8~D15,UDM,UDQS)

- ➤ 信号线的间距满足3W原则

#### **▶DDR的布线**

- > 数据线、地址 (控制) 线、时钟线之间的距离保持20mil以上或至少3W

- > 完整的参考平面

- ▶ VREF电源走线推荐>=20~30mil

- ▶ 误差范围: 差分对误差严格控制在5mil 数据线误差范围控制在+/- 25mil 地址线误差范围控制在+/- 100mil

#### ▶Class规则

将数据类设为2组Class(D0~D7,LDM,LDQS)(D8~D15,UDM,UDQS); 地址线,控制线,时钟线设为1组Class

#### ▶DDRx1片的等长布线

#### >等长规则:

所有信号线参照时钟线的长度等长

#### ▶误差范围:

数据线误差范围控制在+/- 25mil 地址线误差范围控制在+/- 100mil

####

### >DDR的时序设计

▶DDR(采用树形或者星型拓扑)

| DQSL/DQ<br>SH<br>DQ0~DQ1<br>6<br>DQML/DQ<br>MH | 严格等长设计,误差控制在±2  | 25mil  |        |

|------------------------------------------------|-----------------|--------|--------|

| CLK/CLK#                                       | 严格差分等长设计        |        | 尽量控制等长 |

| A0~A11                                         |                 |        |        |

| WE/CAS/R<br>AS                                 |                 | 尽量控制等长 |        |

| BA0/BA1                                        | 等长设计,控制在±100mil |        |        |

| CS#                                            |                 |        |        |

| CKE                                            |                 |        |        |

## 随机存储器-动态RAM DDR2

>DDR VS DDR2

| Memory Type        | DDR                                                   | DDR2                                     |

|--------------------|-------------------------------------------------------|------------------------------------------|

| Core Voltage(VDD)  | 2.5V                                                  | 1.8V                                     |

| I/O Voltage (VDDQ) | SSTL_2(2.5V)                                          | SSTL_1.8(1.8)                            |

| Data Rate          | 200/266/333/400Mbps                                   | 400/533/667/800Mbps                      |

| Bus Frequency      | 100/133/166/200MHz                                    | 200/266/333/400MHz                       |

| Core Frequency     | 100/133/166/200MHz                                    | 100/133/166/200MHz                       |

| Pre-fetch          | 2-bit                                                 | 4-bit                                    |

| Burst Length       | 2/4/8                                                 | 4/8                                      |

| Data Strobe        | Single DQS                                            | Differential DQS, /DQS                   |

| Write Latency      | 1 clock                                               | (Read Latency-1) clock                   |

| CAS Latency        | 1.5, 2, 2.5                                           | 3, 4, 5                                  |

| Package            | x4/x8/x16: 66-pin TSOP(II)<br>x4/x8/x16: 60-ball FBGA | x4/x8: 60 ball FBGA<br>x16: 84 ball FBGA |

| New Features       |                                                       | OCD<br>ODT<br>Posted CAS                 |

DDD ve DDD2

#### Altium 随机存储器-动态RAM DDR2 SDRAM Data Bus DDR SDRAM SDR SDRAM DDR2 Array SDRAM Prefetch 4 bit 2 bit 1 bit DDR I Đạta Freg = 200 MH >DDR VS DDR2 100MHz 100MHz 100MHz Internal bus operating Memory frequency Data Bus 100MHz External clock 200MHz 100MHz Array Buffers frequency Data bus 400Mbps 200Mbps 100Mbps DDR II speed min min Data Bus Buffers Array

## 随机存储器-动态RAM DDR2

#### ▶DDR2的设计

▶DDR新特性:

DDR2可以看做DDR的升级,由于DDR的内部设计使得I/O口的速率最高只能达到200Mhz,而DDR2最高可以提高到400Mhz,也就是DDR2比DDR提高了一倍的速率。在信号管脚上变化的主要是将单端的DQS信号变成了差分的DQS和DQS#。

DQS DQS/DQS#

Clock Frequency

200MHZ(Max) 400MHZ(Max)

- ▶DDR2的布局

- ▶ 布局思路同DDR

## 随机存储器-动态RAM DDR2

#### ▶DDR2数据匹配电阻的布局

>数据匹配电阻应靠近DDR.布线也会容易些。 (数据线是双向传输的,有的核芯不一定有 ODT功能.如有ODT功能匹配电阻放那边都没有 问题,当核芯没有ODT功能匹配电阻靠CPU就有 问题,所以综合考虑匹配电阻应靠DDR放置)

左图SDRAM的数 据线排阻应近 SDRAM直接接上 可以减少过孔.

Figure 8-11 shows the topology and routing for the DQS and DQ net classes; the routes are point to point. Skew matching across bytes is not needed nor recommended.

Figure 8-11. DQS and DQ Routing and Toplogy

Table 8-12. DQS and DQ Routing Specification

| NO. | PARAMETER                                               | MIN     | TYP  | MAX     | UNIT |

|-----|---------------------------------------------------------|---------|------|---------|------|

| 1   | Center-to-center DQS-DQSn spacing in E0 E1 E2 E3        |         |      | 2w      | 1    |

| 2   | DQS-DQSn skew in E0 E1 E2 E3                            |         |      | 25      | Mils |

| 3   | Center-to-center DQS to other DDR2 trace spacing (1)    | 4w      |      |         |      |

| 4   | DQS/DQ nominal trace length (2)(3)(4)                   | DQLM-50 | DQLM | DQLM+50 | Mils |

| 5   | DQ-to-DQS skew length mismatch <sup>(2)(3)(4)</sup>     |         |      | 100     | Mils |

| 6   | DQ-to-DQ skew length mismatch <sup>(2)(3)(4)</sup>      |         |      | 100     | Mils |

| 7   | DQ-to-DQ/DQS via count mismatch <sup>(2)(3)(4)</sup>    |         |      | 1       | Vias |

| 8   | Center-to-center DQ to other DDR2 trace spacing (1)(5)  | 4w      |      |         |      |

| 9   | Center-to-center DQ to other DQ trace spacing (1)(6)(7) | 3w      |      |         |      |

| 10  | DQ/DQS E skew length mismatch (2)(3)(4)                 |         |      | 100     | Mils |

#### ▶DDR2地址线匹配电阻的布局

▶DDR2地址线匹配电阻位置应靠近核芯

## 随机存储器-动态RAM DDR2

#### ▶DDR2的布线

- ▶ 特性阻抗:单端50欧,差分100欧

- ▶ 数据线每11根尽量走在同一层

(D0~D7, DQM0,DQS0 N,DQS0 P)

(D8~D15, DQM1,DQS1 N,DQS1 P)

(D16~D23,DQM2,DQS2\_N,DQS2\_P)

(D24~D31,DQM3,DQS3 N,DQS3 P)

DDR2x1片

❖ 误差范围:

差分对误差严格控制在5mil 数据线误差范围控制在+/-15mil 地址线误差范围控制在+/-100mil

DDR2x2片

➤ 信号线的间距满足3W原则

- ▶ 数据线、地址(控制)线、时钟线之间的距离保持20mil以上或至少3W

- > 完整的参考平面

- ▶ VREF电源走线推荐>=20~30mil

#### ▶DDR2的布线

- ▶ DQGATE组分为低16位和高16位

- DQGATE\_L = DDRCLKOUTP + (DDRDQSOP + DDRDQS1P) / 2

- ▶ 布线拓扑: 布线长度误差控制在100mil

- DQGATE\_H = DDRCLKOUTP + (DDRDQS2P + DDRDQS3P) / 2

## 随机存储器-动态RAM DDR2

#### DDR2 (采用树形或者星型拓扑)

#### ▶DDR2芯片时序设计

| DQSH/DQS<br>H# | 严格差分等长设计                |                  |       |

|----------------|-------------------------|------------------|-------|

| DQSL/DQS<br>L# | 严格差分等长设计                | 严格等长设计,控制在±15mil |       |

| DQ0~DQ16       | 変数をレミルキ もをした            |                  |       |

| DQML/DQ<br>MH  | 严格等长设计,控制在<br>  ± 15mil |                  | 尽量控制等 |

| CLK/CLK#       | 严格差分等长设计                |                  | ₭     |

| A0~A11         |                         |                  |       |

| WE/CAS/RA<br>S | 等长设计,控制在                | <br>             |       |

| BA0/BA1        | ± 100mil                |                  |       |

| CS#            |                         |                  |       |

| CKE            |                         |                  |       |

#### ▶DDR3的设计

▶ DDR3的新特性

DDR3和DDR2在信号定义上基本上是一样的,信号定义上变化很小,大家可以看到有些芯片上会出现两根新的信号TDQS/TDQS#,它只是在8位RAM上会使用到,4位和16位的RAM不会用到他们,所以我们这里不特别阐述,我们可以简单的把它看做单向传输的DQS信号(RAM->Controller),将其和DQS/DQS#,DATA,DM归为一组即可。

### 随机存储器-动态RAM DDR3

#### ▶DDR3与DDR2的比较

| Technology                            | DDR2          | DDR3           |

|---------------------------------------|---------------|----------------|

| Max Clock Freq. (MHz)/Data rate(Mbps) | 533/1066      | 800/1600       |

| Power Requi                           | rement        |                |

| VDD (Volts)                           | 1.8 +/- 0.1   | 1.5 +/- 0.075  |

| Vtt (Volts)                           | 0.9 +/- 0.04  | 0.75 +/- TBD   |

| Vref (Volts)                          | 0.9 +/- 0.018 | 0.75 +/- 0.015 |

| Input Thres                           | holds         |                |

| Vih/Vil (Volts)                       | 0.9 +/- 0.2   | 0.75 +/- 0.175 |

| Delay Matching R                      | Requirement   |                |

| Match ADDR/CMD/CNTRL to Clock tightly | Yes           | Yes            |

| Match DQ<7,0>, DM0 to DQS0 tightly    | Yes           | Yes            |

| Match DQ<15,8>, DM1 to DQS1 tightly   | Yes           | Yes            |

| Match DQ<22,16>, DM2 to DQS2 tightly  | Yes           | Yes            |

| Match DQ<31,23>, DM3 to DQS3 tightly  | Yes           | Yes            |

| Match DQS0-3 to Clock loosely         | Yes           | Not required   |

# Altium.

#### ▶ DDR3与DDR、DDR2的比较

|                                | DDR                 | DDR2                                | DDR3                                |

|--------------------------------|---------------------|-------------------------------------|-------------------------------------|

| 时钟频率                           | 100/133/166/200MHz  | 200/266/333/400MHz                  | 400/533/667/800MHz                  |

| 数据传输速率                         | 200/266/333/400Mbps | 400/533/667/800Mbps                 | 800/1066/1333/1600Mbps              |

| 输入/输出位宽                        | x4/x8/x16/x32       | x4/x8/x16                           | x4/x8/x16                           |

| <b>预取宽度</b> 2位                 |                     | 4位                                  | 8位                                  |

| 突发长度 2,4,8                     |                     | 4, 8                                | 8                                   |

| 数据选通(DQS)                      | 单线                  | 单线/差分                               | 差分                                  |

| 电源电压                           | 2. 5V±0. 2V         | 1.8V±0.1V                           | 1.5V±0.075V                         |

| 接口类型 SSTL_25                   |                     | SSTL_18                             | SSTL_15                             |

| <b>CAS延迟(CL)</b> 2, 2.5, 3时钟频率 |                     | 3, 4, 5时钟频率                         | 5, 6, 7, 8, 9, 10时钟频率               |

| 片内终结器(ODT)                     | 不支持                 | 支持                                  | 支持                                  |

| 封装类型 66pin TSOP2 60pin BGA     |                     | 60pin BGA(x4, x8)<br>84pin BGA(x16) | 78pin BGA(x4, x8)<br>96pin BGA(x16) |

| Write Leveling                 | 不支持                 | 不支持                                 | 支持                                  |

#### Altıum. 随机存储器-动态RAM DDR3 ▶DDR3的等长 >地址线长度要求 Table 8-24. CK and ADDR\_CTRL Routing Specification (1)(2) PARAMETER NO. MAX UNIT A1+A2 length 2500 mils A1+A2 skew A3 length 660 mils A3 skew<sup>(3</sup> 5 A3 skew<sup>(4)</sup> 125 mils A4 length 660 A4 skew AS length AS skew 100 10 AS+/AS- length 70 mils 11 AS+/AS- skew mils 12 AT length 500 mils 13 AT skew<sup>(6)</sup> mils 14 AT skew<sup>(7)</sup> CACLM-50 15 CK/ADDR\_CTRL nominal trace length<sup>(8)</sup> CACLM CACLM+50

# Altium

#### ▶DDR3的等长

> 数据线长度要求

DDR3数据线以

DQS为基准25mil

There are four DQLMs, one for each byte (32-bit interface). Each DQLM is the longest Manhattan distance of the

byte; therefore: DQLM0 = DQLMX0 + DQLMY0 DQLM1 = DQLMX1 + DQLMY1 DQLM2 = DQLMX2 + DQLMY2 DQLM3 = DQLMX3 + DQLMY3

Table 8-25, Data Routing Specification (1)

| NO.                                    | PARAMETER                                                 | MIN | TYP | MAX   | UNIT |

|----------------------------------------|-----------------------------------------------------------|-----|-----|-------|------|

| 1                                      | DB0 nominal length <sup>(2)(3)</sup>                      |     |     | DQLM0 | mils |

| 2                                      | DB1 nominal length <sup>(2)(4)</sup>                      |     |     | DQLM1 | mils |

| 3                                      | DB2 nominal length <sup>(2)(5)</sup>                      |     |     | DQLM2 | mils |

| 4 DB3 nominal length <sup>(2)(6)</sup> |                                                           |     |     | DQLM3 | mils |

| 5                                      | DBn skew <sup>(7)</sup>                                   |     |     | 25    | mils |

| 6                                      | DQSn+ to DQSn- skew                                       | 99  |     | 5     | mils |

| 7                                      | DQSn to DBn skew <sup>(7)(8)</sup>                        | 10  |     | 25    | mils |

| 8                                      | Center-to-center DBn to other DDR3 trace spacing (9)(10)  | 4w  |     |       |      |

| 9                                      | Center-to-center DBn to other DBn trace spacing (9)(11)   | 3w  |     | 30    |      |

| 10                                     | DQSn center-to-center spacing (12)                        | 9.0 |     | - 20  |      |

| 11                                     | DQSn center-to-center spacing to other net <sup>(9)</sup> | 4w  |     | (5)   |      |

- | DGSn center-to-center spacing to other nete\*\*

| External termination disallowed. Data termination should use built-in ODT functionality.

| DGLMn is the longest Manhattan distance of a byte. For definition, see Section 8.3.2.18.2 and Figure 8-39.

| DGLM0 is the longest Manhattan length for the net classes of Byte 0.

| DGLM1 is the longest Manhattan length for the net classes of Byte 1.

| DGLM2 is the longest Manhattan length for the net classes of Byte 2.

| DGLM3 is the longest Manhattan length for the net classes of Byte 2.

| DGLM3 is the longest Manhattan length for the net classes of Byte 2.

| DGLM3 is the longest Manhattan length for the net classes of Byte 3.

| Length matching is only done within a byte. Length matching across bytes is neither required nor recommer Each DGS pair is length matched to its associated byte.

| DGS pair is length matched to its associated byte.

| Center-to-center spacing is allowed to fall to minimum for up to 1.250 mils of routed length.

| Other DGR3 trace spacing means other DGR3 net classes not within the byte.

| DGS pair spacing is set to ensure proper differential impedance.

## 随机存储器-动态RAM DDR3

#### ▶DDR3的拓扑结构

DDR3的地址拓扑和DDR2, DDR一样, 只是由 于其速率更高(最高可达到1.6Gbps), 所以除了 时序,信号完整性也成了我们需要关注的要点, 前文提到的在多片DDR设计时采用的4种拓扑, 我们在进行DDR3设计,尤其是当速率跑到 1.6Gbps时,通过仿真我们发现4种拓扑中只有D, 即菊花链拓扑满足信号完整件要求,但是这里并 不是说其他3种拓扑不适用,只是在满足时序要 求的情况下, D型拓扑能最好的达到信号完整件 的要求。

#### ▶DDR3的拓扑结构

## 随机存储器-动态RAM DDR3

#### ▶DDR3的布局布线实例

▶ 地址线布局布线要求优选F ly-By, 过孔到管脚长度尽量短, 长度在150mil左右

- ▶DDR3的布局布线实例

- ▶8颗DDR3正反对贴布线示例

## 随机存储器-动态RAM DDR3

- ▶DDR3芯片设计总结

- ▶DDR3(采用树形或菊花链拓扑)

| A0~A11     | J在士10mil                                |            | 尽量控制等<br>长 |

|------------|-----------------------------------------|------------|------------|

| BA0/BA1 制在 | 差分等长设计<br>控制等长,控<br>E±100mil如<br>菊花链拓扑则 | 尽量控制等<br>长 | X.         |

#### DDR4新特点:

- 一. **8**位预读取,外部时钟频率是内部时钟频率的八倍,数据传输率最高可达**3**.**2**Gbps;

- 二. 内核电压仅为1.2V;

布局布线要求基本同DDR3:

等长要求(推荐以Layout Guide为准、以仿真结果为准):

- 一. 数据线最大长度尽量不超过2500mil,组内长度误差范围控制在+/-5mil,得益于Write Leveling技术,DQS与时钟线一般无长度误差要求,注意尽量查阅Layout Guide或datasheet,部分芯片会有组间、以及DQS与时钟线的等长要求;

- 二. 地址线误差范围控制在+/-20mil:

- 三. DQS、时钟差分对内误差范围控制在+/-3mil,设计阻抗时,使本对内间距不超过2倍线宽;

#### 随机存储器-动态RAM RDRAM

- ➤ RDRAM是由R ambus公司推出的一种采用双沿触发技术的内存,有16/18bit (ECC)两种规格,能在很高的频率范围内通过一个简单的总线传输数据

- > 功能管脚说明

| 信号名                       | 类型    | 电平   | 功能描述                                                        |

|---------------------------|-------|------|-------------------------------------------------------------|

| DQA (8: 0)                | 10    | RSL  | 数据字节 A。在通道与 RDRAM 器件间进行一个字节的数据信号传递。在 x16 的系統中 DQA (8) 将不使用。 |

| DQB (8: 0)                | 10    | RSL  | 数据字节 B。在通道与 RDRAM 器件间进行一个字节的数据信号传递。在 x16 的系統中 DQB(8) 将不使用。  |

| RQ (7: 5) 或<br>ROW (2: 0) | Input | RSL  | 行访问控制。传递行访问的控制与地址信号。                                        |

| RQ (4: 0) 或<br>COL (4: 0) | Input | RSL  | 行访问控制。传递行访问的控制与地址信号。                                        |

| CFM, CFMN                 | Input | RSL  | Clock From Master。从通道中接收 RSL 信号的差分接口时钟。                     |

| CTM, CTM#                 | Input | RSL  | Clock To Master。发送 RSL 信号到通道的差分接口时钟。                        |

| CMD                       | Input | CMOS | 串行命令輸入。与 SI00 和 SI01 一起用于读写控制寄存器, 也用于电源管理。                  |

| SCK                       | Input | CMOS | 串行时钟输入。用于读写 RDRAM 控制寄存器的时钟源。                                |

| SI01, SI00                | 10    | CMOS | 串行輸入輸出。通过串行协议读写控制寄存器,也用于<br>电源管理。                           |

| Vref                      |       | DC   | RSL 信号的逻辑门限参考电压。                                            |

| Vcmos                     |       | DC   | CMOS 輸入輸出管脚的电源电压。                                           |

| Vdda                      |       | DC   | RDRAM 模拟电路的电源电压。                                            |

| Vdd                       |       | DC   | RDRAM 内核与接口逻辑的电源电压。                                         |

| GNDa                      |       | DC   | RDRAM 模拟电路的地参考。                                             |

| GND                       |       | DC   | RDRAM 内核与接口逻辑的地参考。                                          |

## 随机存储器-动态RAM RDRAM

Altıum.

➤ RDRAM与 SDRAM架构 比较

#### 特点:

- 1.信号线数目较少,所有信号均为串联接法;

- 2.工作频率极高, 所有RSL电平信号都要包地, 并以地平面为参考:

- 3.DQ、RQ、和CTM、SCK、CMD等信号的走线长度在分段过程中每一段的长度都必须匹配,匹配的计算不仅包括走线,还句括管脚长度,误差挖制在+/-10mi1以内;

### 随机存储器-静态RAM SRAM

#### > SRAM的特点

- >SRAM是Static RAM缩写,即静态随机存储器,它是一种具有静止存取功能的内存,不需要刷新电路就能保持内部存储数据的有效性,但断电后,数据仍然会丢失

- ▶SRAM存取速度快,但比相同容量的DRAM体积大,功耗也大,因此目前 单片SRAM容量一般都是几百K到几十M

## 随机存储器-静态RAM SRAM

## **▶SRAM**的特点

➤右图为SRAM,目前 SRAM运用较为广泛的是 QDR SRAM系列

# 随机存储器-静态RAM QDR

# ➤ QDR的设计

▶ QDR的新特性: 可在一个时钟周期内传送四次数据(两次读与两次写数据)

| 信号名。                    | 功能描述。                     |

|-------------------------|---------------------------|

| К, К#                   | 输入时钟。。                    |

| C, C#0                  | 用于输出数据的输入时钟。。             |

| SA <sub>e</sub>         | 地址信号输入。。                  |

| D0-17 (35) o            | 数据信号输入。。                  |

| Q0-17 (35) <sub>o</sub> | 数据信号输出。*                  |

| ₩# <sub>\$</sub>        | 写操作控制信号。。                 |

| R#.                     | 读操作控制信号。。                 |

| BW0#- BW 1 (3) #.       | 字节写控制信号。。                 |

| Vref.                   | 输入参考电平。。                  |

| ZQ <sub>e</sub>         | 输出驱动器阻抗控制端。。              |

| VDD.                    | 电源电压 (2.5V)。。             |

| VDDQ <sub>o</sub>       | 输出 IO 电源电压 (1.5V 或 1.8V)。 |

| VSS.                    | 地管脚。。                     |

| TMS, TCK, TDI, TDO      | JTAG 测试模式控制管脚。。           |

# 随机存储器-静态RAM QDR PQDR的布局 P布局与DDR类似 A型

# 随机存储器-静态RAM QDR

B型

#### **▶QDR的布局**

▶布局与DDR类似

# 随机存储器-静态RAM QDR

#### **▶QDR**的时序设计

| 7 | QDR信号数据信号   | QDR_0_D0-17     | 组内信号误差25mi1正负 |

|---|-------------|-----------------|---------------|

|   |             | QDR_0_Q0-17     |               |

| 8 | QDR信号时钟信号   | QDR_O_K         | 时钟差分误差小于10mil |

|   |             | QDR_O_K_N       | 不同差分对尽量等长     |

|   |             | QDR_O_C         |               |

|   |             | QDR_0_C_N       |               |

|   |             | QDR_O_CQ        |               |

|   |             | QDR_O_CQ_N      |               |

| 9 | QDR地址命令控制信号 | QDR_0_A0-18     | 尽量等长          |

|   |             | QDR_O_BWNO      |               |

|   |             | QDR_O_BWN1      |               |

|   |             | QDR_O_RN        |               |

|   |             | QDR_O_WN        |               |

|   |             | QDR_0_ZQ        |               |

|   |             | QDR_0_DLL_OFF_N |               |

#### 随机存储器-静态RAM QDR

QDR2 SRAM规范中要求K/K#时钟和C/C#时钟的偏移必须大于0,因为QDR的同时读写特点,假设在同一时钟周期内,要对同一个地址的数据进行读操作和写操作,规范要求是,要先进行写操作,后进行读操作,也就是写参考时钟K/K#需要比读参考时钟C/C#先到达。但是,规范中同时规定,C/C#时钟与K/K#时钟之间的skew必须小于三分之一时钟周期。

因此如果将多片QDR2 SRAM器件并联使用的并且有C/C#时钟的话,需要注意C/C#时钟的PCB走线方式,即C/C#时钟须先到达最远端的QDR器件,最后到达最近处的QDR器件,这样,参考时钟信号的延迟正好可以抵消数据信号的延迟,确保几个器件上的数据保持同步,如下图所示。

#### 随机存储器-静态RAM QDR

QDR2等长要求(推荐以Layout Guide为准、以仿真结果为准):

- 一. 输入时钟K/K#和写数据信号D[17:0]设为一个组等长,组内误差+/-25mil;

- 二. 输出时钟CQ/CQ#和读数据信号Q[17:0]设为一个组等长,组内误差+/-25mil;

- 三. 其他地址信号和控制信号设为一个组等长,组内误差+/-50mil,同时与系统时钟K/K#误差+/-100mil,与数据组误差+/-100mil;

- 四. 差分线组内误差+/-5mil;

其实由上述规则可以看出,读、写数据和地址、控制信号,以及输入输出时钟是存在时序关系的,因此,在等长设定时可将左右信号设成一个组等长,误差设为+/-25mil:

Altıum.

#### DDR4

| Specification            | DDR2     | DDR3         | DDR4      |

|--------------------------|----------|--------------|-----------|

| Voltage                  | 1.8 V    | 1.5 / 1.35 V | 1.2 V     |

| Per Pin Data Rate (Mbps) | 400-1066 | 800-2133     | 1600-3200 |

3.2-8.5

512 MB-2 GB

Lower VDD voltage and Pseudo-Open Drain (POD) reduces power consumption by 40%

Channel Bandwidth (GBps)

Component Density

- Internal VREF training performed within the IC receiver, to optimize VREF level. Retraining at regular intervals.

- Data lines are calibrated at the IC, to reduce their skew to the strobe.

- Data bus inversion (DBI)

12.8-25.6

2-16 GB

DDR3 Push-Pull

6.4-17

1-8 GB

DDR4 Pseudo-Open Drain

#### Altıum. DDR4 **DDR4 High Speed => Less Timing Margin** Shrinking Timing Margins in Picoseconds ■ DRAM Margin Package / Board Margin Chip Margin → Data Valid Window 2,500 Package/ Data Valid DRAM Board Window Margin Margin Margin DDR1 2,500 900 800 800 DDR2 938 425 256 256 DDR3 469 188 140 140 DDR4 125 313 938 313 DDR1 DDR2 DDR4 DDR3 3,200 Mbps 400 Mbps Image Source: Altera

#### DDR4

|                          | DDRx SDRAM参数 |          |            |            |                |                                |

|--------------------------|--------------|----------|------------|------------|----------------|--------------------------------|

|                          | DDR          | DDR2     | LPDDR2     | DDR3       | LPDDR3         | DDR4                           |

| 速率(Mbps)                 | 200 ~ 400    | 400 ~800 | 333 ~ 1066 | 800 ~ 2133 | 1333 ~<br>2133 | 1600~3200 (SE)<br>~6400 (Diff) |

| VDDQ(V)                  | 2.5          | 1.8      | 1.2        | 1.5        | 1.2            | 1.2                            |

| 电平接口                     | SSTL_2       | SSTL_18  | HSUL_12    | SSTL_15    | HSUL_12        | POD12                          |

| 选通信号                     | 单端           | 可选单端/差分  | 差分         | 差分         | 差分             | 差分                             |

| ODT                      | 无            | 有        | 无          | 有          | 可选             | 有                              |

| Slew<br>RateDerati<br>ng | 有            | 有        | 有          | 有          | 有              | 无                              |

| WriteLeveli<br>ng        | 无            | 无        | 无          | 有          | 有              | 有                              |

| DBI                      | 无            | 无        | 无          | 无          | 无              | 有                              |

# DDR4

#### DDR3 新功能

- DDR3新增的重置(Reset)功能

- □ DDR3新增ZO校准功能

- □ 突发长度(Burst Length, BL),由于DDR3的预取为8bit,所以突发传输周期(Burst Length, BL)也固定为8

- □ 寻址时序(Timing)变化

- ① 参考电压分成两个VREF将分为两个信号,即为命令与地址信号服务的VREFCA和为数据总线服务的REFDQ,这将有效地提高系统数据总线的信噪等级

#### DDR4

#### DDR4 新功能

- □ 新的JEDEC POD12接口标准(工作电压1.2V);

- □ DBI: 可以降低功耗并且提升数据信号完整性;

- □ Bank群组结构: 是个8n预取群组结构,它可以使用两个或者四个Bank组,这允许DDR4内存在每个Bank群组单独被激活、读取、写入或刷新操作,这样可以带来更高的内存速度和带宽;

- □ 取消了Derating,时序仿真计算不再繁琐;

- □ DQ动态确定Vref(V\_center),增加了眼图要求;

- □ 新的终止调度:在DDR4中DQ bus可以转移终止到VDDQ,这样即使VDD电压降低的情况下也能保证稳定:

- □ 新的数据总线CRC技术,可以进行传输过程中的错误侦测,特别对非ECC内存进行写入操作时有帮助;

- □ 针对命令和地址总线的新的CA奇偶校验:

- □ 突发长度和突发停止长度分别为8和4;

- □ 正常和动态的ODT:改进ODT协议,并且采用新的Park Mode模式可以允许正常终结和动态吸入终结,而不需要去驱动ODT Pin;

- □ \*Differential Signaling(差分信号技术)

# **DDR4 vs DDR3**

| 特点         | DDR3                              | DDR4                               | 备注                |  |  |

|------------|-----------------------------------|------------------------------------|-------------------|--|--|

|            | 信令变化                              |                                    |                   |  |  |

| 电压(内核和I/0) | 1.5V                              | 1.2V                               | 降低能耗              |  |  |

| 低压标准       | 是(DDR3L@ 1.35V)                   | 预计(DDR4L,可能1.05V)                  | 内存能耗下降            |  |  |

| 数据速率(MT/s) | 800, 1066, 1333, 1600, 1866, 2133 | 1600, 1867, 2133, 2400, 2667, 3200 | 演进到更高速度           |  |  |

| 密度         | 512Mb - 8Gb                       | 2Gb -16Gb                          | 满足更高容量的内存<br>需求   |  |  |

| DBI        | 无                                 | 有                                  | 更低功耗和更好的信<br>号完整性 |  |  |

| DQ驱动器(ALT) | 40欧姆                              | 48欧姆                               | 为点到点应用优化          |  |  |

| DQ总线       | SSTL 15                           | POD 12                             | 降低I/0噪声和能耗        |  |  |

| RTT值       | 120, 60, 40, 30, 20               | 240, 120, 80, 60, 48, 40, 34       | 支持更高的数据速          |  |  |

| 堆叠引脚       | 否                                 | 是                                  | 适用于未来的更高密<br>度的模块 |  |  |

# DDR4 Skew/等长

|                                                                                                        | DDR3                                                     | DDR4                                            |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------|

|                                                                                                        | 同组DQ/ECC与对应DQS等长保持在100mi1内                               | 同组DQ/ECC与对应DQS等长保持在50mi1内                       |

| Course-Cunchnonous Ciemal                                                                              | DQS 差分线对内等长保持在5mi1内                                      | DQS 差分线对内等长保持在5mi1内                             |

| Source-Synchronous Signal                                                                              | 司组DQ/ECC等长保持在30mi1内                                      | 同组DO/ECC等长保持在10mi1内                             |

|                                                                                                        | 同组信号严格要求同层走线                                             | 同组信号严格要求同层走线                                    |

| Clock Signal                                                                                           | CLK差分线对内等长保持在2mi1内                                       | CLK差分线对内等长保持在2mi1内                              |

| Clock Signal                                                                                           | 同一DIMM的CLK之间等长保持在20mi1内                                  | 司一DIMM的CLK之间等长保持在5mi1内                          |

| Source Clocked<br>Signal (MA[15:00], BA[2:0], RA<br>S_N, CAS_N, WE_N, MA_PAR)/BG<br>[1:0], ACT_N, C[2] | 同一个DLL组.CMD要求等长保持在500mil内所有CMD信号要求与对应时钟保持在2inch内         | 同一个DLL组,CMD要求等长保持在25mi1内所有CMD信号要求与对应时钟保持在2inch内 |

| Source Clocked<br>SignalCS_N[9:0], ODT[5:0], CK<br>E[5:0]                                              | 同一个DLL组, UDIMM CTL要求与时钟等长保持在100mil内, for RDIMM保持在240mil内 | 同一个DLL组,CTL要求与时钟等长保持在25mi1内,for RDIMM保持在100mi1内 |

DDR3摘自Intel Romley PDG; DDR4摘自Intel Grantley PDG

# DDR4 Crosstalk/串扰

|                                                                                                | DDR3                                                                                              | DDR4                                                                                                    |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|                                                                                                | 同组DO/ECC/DOS最小间距:内层17mil(4.25H)外层19mil(7.03H)                                                     | 同组DO/ECC/DOS最小间距:内层17mil(4.25H)外<br>层19mil(7.03H)                                                       |

| Source-Synchronous Signal                                                                      | 组间DQ/ECC最小间距: 内层32mil,外层27mil                                                                     | 组间DQ/ECC最小间距:内层32mil,外层27mil                                                                            |

| 30urce-synchronous signal                                                                      | 同层通道间DQ/ECC最小间距:内层40mil,外层32mil                                                                   | 同层通道间DQ/ECC最小间距:内层40mil,外层32mil                                                                         |

|                                                                                                | DQ/ECC在DIMM Pin处间距: 内层9mil,外层12mil                                                                | DQ/ECC在DIMM Pin处间距:内层17mil,外层<br>19mil                                                                  |

| Clock Signal                                                                                   | CLK差分线对内间距5mil                                                                                    | CLK差分线对内间距5mil                                                                                          |

| Clock Signal                                                                                   | CLK差分线与其他信号间距:内层12mil,外层13.5mil                                                                   | CLK差分线与其他信号间距:内层12mil,外层<br>13.5mil                                                                     |

| Source Clocked<br>Signal(MA[15:00],BA[2:0],RA<br>S_N,CAS_N,WE_N,MA_PAR)/<br>BG[1:0],ÄCT_N,C[2] | CMD信号之间间距:内层12mil,外层13.5milCMD信号与DQ信号最小间距:内层32mil,外层27milCMD信号在DIMM Pin处间距:内层9mil,外层12mil         | CMD信号之间间距:内层12mil,外层13.5milCMD信号与DQ信号最小间距: 内层32mil,外层27milCMD信号在DIMM Pin处间距: 内层4.9mil,外层6.9mil          |

| Source Clocked<br>signalCS_N[9:0],ODT[5:0],CK<br>E[5:0]                                        | CTL信号之间间距内层12mil,外层13.5milCTL信号<br>与DC信号最小间距: 内层32mil,外层27milCTL信号<br>在DIMM Pin处间距:内层9mil,外层12mil | CTL信号之间间距: 内层12mil,外层13.5milCTL信号<br>与DC信号最小间距: 内层32mil,外层27milCTL信号<br>在DIMM Pin处间距: 内层4.9mil,外层6.9mil |

DDR3摘自Intel Romley PDG; DDR4摘自Intel Grantley PDG

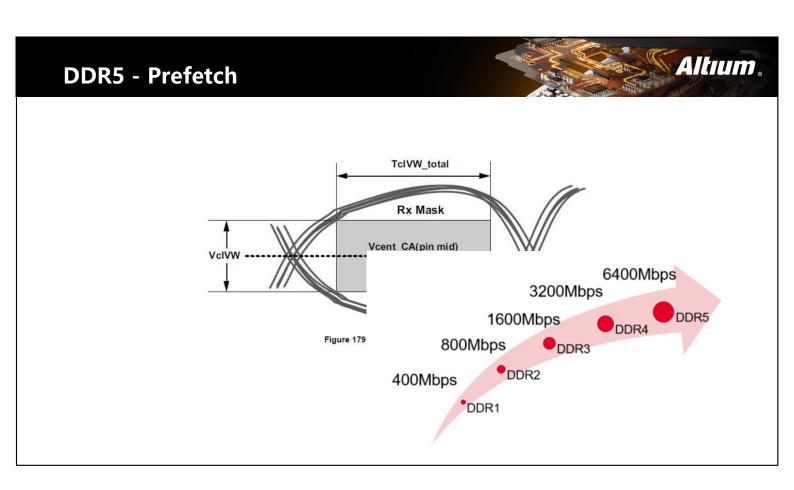

# DDR5 vs DDR4

| 对比项目     | DDR4      | DDR5      |

|----------|-----------|-----------|

| 速率       | 1.6G~3.2G | 3.2G~6.4G |

| 电压       | 1.2V      | 1.1V      |

| 均衡       | 无         | 有         |

| ODT      | DQ        | DQ,CA     |

| Prefetch | 8n        | 16n       |

| BL       | BL8       | BL16      |

| 单颗DRAM容量 | 16Gb      | 32Gb      |

Altıum.

# **DDR5** - Burst length

Altium.

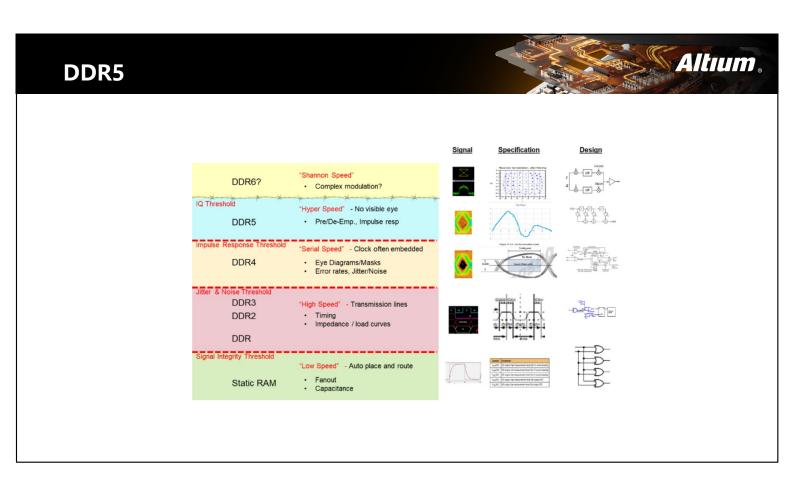

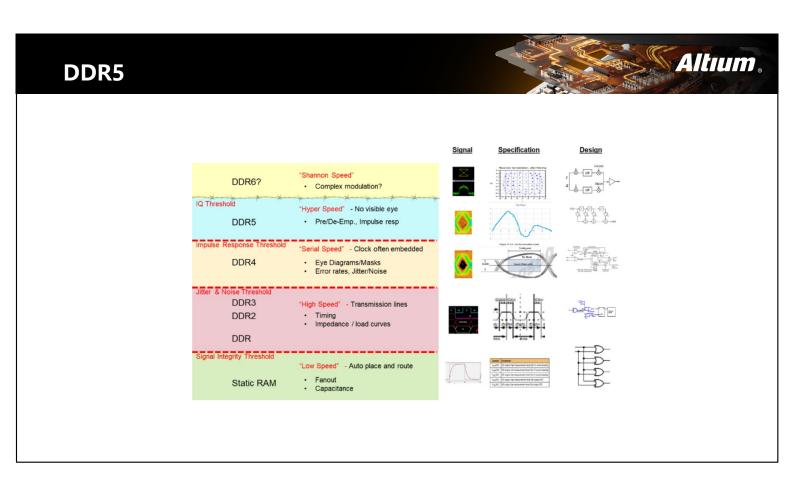

# DDR5

# DDR5特点

2.更宽的总线,单端信号,从RCD(Registering ClockDrivers)芯片来看采用Multi-Drop架构。

基于今天更宽的总线需求,在一块刀片服务器上可能支持1000+个并行数据通道。且由于继续采用单端信号且速率倍增,传统只在串行差分电路上考虑的损耗问题也开始困扰DDR5.因此在DDR5设计和验证测试上,不仅需要考虑传统的串扰问题还增加了对电路损耗问题的考虑

Altıum.

# 只读存储器ROM-FLASH

Altıum.

- ➤ FLASH特点

- ▶ 速率较低,通常在50Mhz以下

- ▶ 静态存储

- > 布局

- > 一般采用菊花链

- > Flash和SDRAM的推荐距离为500-1000mil

# 只读存储器ROM-FLASH

- > 特性阻抗:50欧

- > 线间距3W

- > 等长范围:+/-100mil

#### 只读存储器ROM-EEPROM电路概述

#### **EEPROM**

EEPROM(电可擦可编程只读存储器)这是一种具有可擦除功能,擦除后即可进行再编程的ROM内存,一种掉电后数据不丢失的存储芯片,EEPROM可以在电脑上或专用设备上擦除已有信息,重新编程。这类芯片一般用于即插即用。

# 只读存储器ROM-EEPROM典型电路

Vcc

- 1.在某些器件中,引脚A0,A1,A2在内部未连接

- 2.应使用一个去耦合电容(通常为0.1UF)来帮助滤除VCC上的小纹波

# 只读存储器ROM-EEPROM典型电路

1.2.3: A0 A1 A2 器件地址选择

5: SDA 串行数据,地址

▶ 管脚定义 6: SCL 串行时钟

7: WP 写保护

8: VCC +1.8V~6.0V工作电压

# 只读存储器ROM-EEPROM布局要求

> 靠近主芯片放置,使距离尽量短

# 只读存储器ROM-EEPROM布线要求

#### **EEPROM**电路布线要求

- (1) 控制50欧姆阻抗。

- (2) 两根线并行走,与其他信号线保持3W以上的间距。

- (3) 尽量在表层走线;如需换层,需要有完整的参考平面,保持阻抗 连续性;并保证过孔数量不超过3个。

且在换层处100mil以内添加一个或者两个回流地孔。

# 随机存储器-动态RAM SDRAM

#### > SDRAM (同步动态随机存储器)

#### > 管脚定义解释

| 信号名。             | 功能描述。    |

|------------------|----------|

| CLK.             | 时钟。      |

| CKE.             | 时钟使能。    |

| CS#.             | 片选。      |

| WE#.             | 读写。      |

| RAS#.            | 列选。      |

| CAS#.            | 行选。      |

| DQM <sub>e</sub> | 数据掩码。    |

| BAO, BA1.        | Bank 选择。 |

| A 0-A 1 1.       | 地址。      |

| DQ 0-DQ 1 5.     | 数据(输出)。  |

| VDDQ.            | DQ 电源。   |

| VSSQ.            | DQ 地。    |

| VDD.             | 电源。      |

| VSS.             | 地。       |

# 随机存储器-动态RAM SDRAM

- ➤ SDRAM的布局原则: 靠近CPU放置

- > SDRAM X 1片时:点对点的布局方式

- > SDRAM到CPU的中心距离为:

当中间无排阻时: 900-1000mil 当中间有排阻时: 1000-1300mil

#### 随机存储器-动态RAM SDRAM

#### ➤ SDRAM的布局原则:

➤ SDRAM X 2片时:相对于CPU严格对称

方案一: 顶底对贴(推荐)

方案二:与CPU放在同一面

# 随机存储器-动态RAM SDRAM

# Altium.

#### > SDRAM的布线

- > 特性阻抗:50欧姆

- ▶ 数据线每9根尽量走在同一层(D0~D7,LDQM;D8~D15,HDQM)

- > 数据线、地址(控制)线、时钟线之间的距离保持20mil以上或至少3W

- ➢ 空间允许的情况下,应该在它们走线之间加一根地线进行隔离。地线宽度推荐为15-30mil

- > 完整的参考平面

- ➤ 布线拓扑结构(默认采用远端分支)-T点(过孔)打在两片SDRAM中间

# Altium. 随机存储器-动态RAM SDRAM > SDRAM的拓扑结构 远端分支(星形/T形) 菊花链 - 地址控制线 • 地址控制线 - 数据线时钟线 数据线时钟线

# 随机存储器-动态RAM SDRAM

- >SDRAM的等长布线

- > Class规则:

将所有数据线设为sdram\_data\_bus; 地址线,控制线,时钟线设为sdram\_addr\_bus

> 等长规则:

所有信号线参照时钟线的长度等长

> 误差范围:

数据线误差范围控制在+/- 50mil 地址线误差范围控制在+/- 100mil

Altıum.

# 随机存储器-动态RAM DDR

#### >DDR的设计

管脚定义解释

| 管脚数₽            | 信号名。            | 功能描述。            | ¢3  |

|-----------------|-----------------|------------------|-----|

| 20              | CK, CK#         | 全局时钟输入。₽         | ÷   |

| 10              | CKE.            | 时钟使能信号输入。。       | t)  |

| 10              | CS#ø            | 片选信号输入。₽         | 4J  |

| 3₽              | RAS#, CAS#, WE# | 命令信号输入。₽         | 47  |

| 20              | LDM, UDM        | 数据 mask 信号输入。→   | 42  |

| 13*₽            | A<012>+         | 地址信号输入。。         | 47. |

| 2₽              | BA0, BA1        | BANK 选择信号输入。。    | 42  |

| 16*₽            | DQ<015>@        | 数据信号输入/输出。₽      | φ   |

| 2₽              | LDQS, UDQS      | 数据锁存信号输入/输出。↩    | 47  |

| 5* <sub>0</sub> | NC.             | 空引脚。。            | 47  |

| 2₽              | DNU₽            | 不使用引脚。 🗸         | 47  |

| 5₽              | VDDQ₽           | DQ 电源电压 (2.5V)。₽ | 47  |

| 5₽              | VSSQ₽           | DQ 地。→           | 47  |

| 3≠              | VDDø            | 器件电源电压 (2.5V)。↓  | 47  |

| 3≠              | VSS.            | 器件地。。            | 47  |

| 1₽              | VREF₽           | SSTL_2 参考电压。₽    | 47  |

DDR SDRAM 封装结构图+

DDR SDRAM 管脚功能说明。

#### 随机存储器-动态RAM DDR

- ❖ 工作原理:

- 一. DDR的读写操作时序如图 所示。图中,命令信号与 地址信号参考CK信号上升 沿输入到DDR。

- 二. 读数据时DQ随着DQS并参考DQS信号沿输出,写数据时DQ随着DQS并参考DQS的信号沿输入,读写数据时DQS都是双沿有效。

- 三. 读数据时,输出的DQS由 送入DDR的差分时钟 CK/CK#使用DDR存储器 中的一个DLL生成DQS, 并使之与输出数据对齐。

- 四. 虽然DDR存储器不用差分 输入时钟来发送或接收数 据,但是所用DQS信号与 输入时钟的频率有关。

Altıum.

# 随机存储器-动态RAM DDR

#### ➤ DDR的布局

- ▶ 布局原则是:靠近CPU摆放

- ▶ DDRx1片时,点对点的布局方式

- ▶ DDR到CPU推荐的中心距离:

当中间无排阻时: 900-1000mil

当中间有排阻时: 1000-1300mil

# Altıum. 随机存储器-动态RAM DDR **▶DDR的布局** ▶DDRx2片时,相对于CPU严格对称 X < 1660milVREF旁路电容 Y < 1280mil Y1 = Y2 < 650mi1**▶VREF电容的位置** A1方向 CPU A1方向 DDR

#### >DDR保护区域

DDR2 保护区域 (Keepout Region): DDR2 内存组,所有同 DDR 相关的阻容电路,一直向 CPU 方向延伸至 CPU 的 DDR 控制器,称为 DDR 保护区域(DDR Keepout Region)。这个区域里需满足以下条件:

- a) 不得出现与 DDR 无关的信号。

- b) 必须提供完整的地平面(信号线下方地平面不得中断)。

- c) 必须提供完整的 VCC\_1V8 电源平面 (信号线下方电源平面不得中断)。

#### 随机存储器-动态RAM DDR

- > 特性阻抗:单端50欧,差分100欧

- 数据线每10根尽量走在同一层 (D0~D7,LDM,LDQS)(D8~D15,UDM,UDQS)

- ➤ 信号线的间距满足3W原则

#### **▶DDR的布线**

- > 数据线、地址 (控制) 线、时钟线之间的距离保持20mil以上或至少3W

- > 完整的参考平面

- ▶ VREF电源走线推荐>=20~30mil

- ▶ 误差范围: 差分对误差严格控制在5mil 数据线误差范围控制在+/- 25mil 地址线误差范围控制在+/- 100mil

#### ▶Class规则

将数据类设为2组Class(D0~D7,LDM,LDQS)(D8~D15,UDM,UDQS); 地址线,控制线,时钟线设为1组Class

#### ▶DDRx1片的等长布线

#### >等长规则:

所有信号线参照时钟线的长度等长

#### ▶误差范围:

数据线误差范围控制在+/- 25mil 地址线误差范围控制在+/- 100mil

####

#### >DDR的时序设计

▶DDR(采用树形或者星型拓扑)

| DQSL/DQ<br>SH<br>DQ0~DQ1<br>6<br>DQML/DQ<br>MH | 严格等长设计,误差控制在±2  | 25mil  |        |